Dieses deutsch-französische Kooperationsprojekt wird durch die Deutsche Forschungsgemeinschaft (DFG) und die Agence Nationale de la Recherche (ANR) gefördert.

Daten- und Signalverarbeitungsanwendungen mit hohen Durchsatzanforderungen lassen sich bevorzugt spezifizieren durch Datenflussnetzwerke, denn diese erlauben die Ausnutzung von Parallelismus global (auf der Ebene des Netzwerks kommunizierender Aktoren) als auch lokal innerhalb eines Aktors, beispielsweise durch Hardwarerealisierung. Es existieren zwar einige Entwurfswerkzeuge, um Datenflussnetzwerke auf ein Multiprozessorsystem zu übersetzen oder alternativ ein Netz direkt in Hardware zu synthetisieren, um einen hohen Datendurchsatz zu erzielen. Eingebettete Systeme, speziell im Kontext von IoT, haben jedoch zusätzliche Anforderungen: Funktionale Sicherheit im Betrieb, insbesondere auch in Umgebungen mit Spannungsunterbrechungen sowie extrem niedrige Verlustleistungen. Diese Anforderungen erscheinen grundsätzlich gegensätzlich.

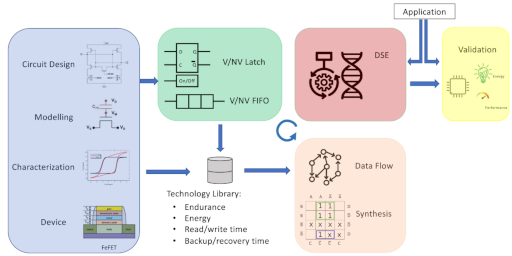

Unser Forschungsprojekt HiLoDa (High performance, (ultra-Low) power Dataflow) Nets greift diese Diskrepanzen und Konflikte der Anforderungen auf durch a) Ausnutzung und Integration emergenter FeFET-Technologie für den Entwurf von Netzwerken, speziell durch Untersuchungen zu und Entwurf von persistierbaren FIFO-Speichern. Dies umfasst die b) Modellierung, Charakterisierung und den Entwurf von Schaltungen, die in einem gemischt flüchtig/nichtflüchtigem Betrieb arbeiten können. Durch Kombinieren des Konzepts von Datenfluss, das auf der selbsttätigen Aktivierung von Berechnungen beruht, mit emergenter CMOS-kompatibler FeFET-Technologie, sollen inaktive Aktoren oder selbst Teilnetze die Fähigkeit erlangen, sich selbst hoch- und herunterzufahren, um Energie zu sparen. Darüber hinaus soll funktionale Sicherheit erreicht werden durch ein autonomes gesichertes Herunterfahren im Falle intermittierenden Spannungsunterbrechungen. Analog sollen Aktoren selbst wieder aufwachen bei Wiederkehr der Versorgungsspannung, aber auch nur dann, wenn zusätzlich auch Daten zu verarbeiten sind.

HiLoDa Nets sollen höchsten Datendurchsatz für die synthetisierten Aktorschaltungen gewährleisten im eingeschalteten Betrieb sowie Sicherheit durch eine automatische Zustandssicherung durch FeFeT-basierte FIFO-Speicher im ausgeschalteten Betrieb, der auch im Falle der Nichtverfügbarkeit von Daten selbstgetriggert erfolgen soll. d) Eine durchgängige Synthese von Datenflussmodellen auf optimierte Netzimplementierungen in Hardware unter Einsatz von FeFeT-Speichern sollen entwickelt werden. Dies beinhaltet e) die Entwurfsraumexploration (DSE) von Clusterbildungen von Aktoren in individuelle Power-Domänen zur Optimierung von Durchsatz, Schaltungskosten, Energieeinsparungen und Beständigkeit. Schließlich sollen HiLoDa Nets verglichen werden mit Implementierungen konventioneller CMOS-Technologie hinsichtlich Energieverbrauch für beispielsweise gepulste neuronale Netzwerke. Gleichsam sollen die Latenzen für das Abschalten und Hochfahren evaluiert und optimiert werden.

HiLoDa Nets – cross-layer hardware synthesis design flow

Publikationen

2025

- , , , , , , :

Non-Volatile Ferroelectric-AND (FeAND) Memory Cell Design

IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC 2025) (Puerto Varas, 12. Oktober 2025 - 15. Oktober 2025)

BibTeX: Download - , , , , , , , :

FeMFET-based High Performance, Ultra-Low Power Memory Cells for Reliable State Retention of Dataflow Networks

38th IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems; Special Session (Barcelona, Spain, 21. Oktober 2025 - 23. Oktober 2025)

In: Proceedings of the 38th IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems 2025

BibTeX: Download - , , :

Exploration of Clock and Power Gating Tradeoffs for the Design of Self-Powering Dataflow Networks

28. Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen (MBMV) (Rostock Warnemünde, 11. März 2025 - 12. März 2025)

In: VDE ITG; VDE/VDI GMM; GI (ed.): Proceedings of the 28th Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen, Berlin - Offenbach: 2025

BibTeX: Download

2024

- , , , :

Self-Powering Dataflow Networks – Concepts and Implementation

22nd ACM-IEEE International Symposium on Formal Methods and Models for System Design (MEMOCODE) (Raleigh, NC, 3. Oktober 2024 - 4. Oktober 2024)

In: Proceedings of the 22nd ACM-IEEE International Symposium on Formal Methods and Models for System Design (MEMOCODE) 2024

DOI: 10.1109/MEMOCODE63347.2024.00013

BibTeX: Download - :

Techniques for Efficient Performance Analysis and Memory Optimization in Mapping Dataflow Models of Computation onto Embedded Systems (Dissertation, 2024)

DOI: 10.25593/open-fau-1040

URL: https://open.fau.de/handle/openfau/31834

BibTeX: Download - , , :

Exploring Multi-Reader Buffers and Channel Placement during Dataflow Network Mapping to Heterogeneous Many-core Systems

In: IEEE Access 12 (2024), p. 39748-39769

ISSN: 2169-3536

DOI: 10.1109/ACCESS.2024.3375079

BibTeX: Download

2023

- , , , , , , , , , , , , , , , :

Special Session - Non-Volatile Memories: Challenges and Opportunities for Embedded System Architectures with Focus on Machine Learning Applications

International Conference on Compilers, Architectures, and Synthesis for Embedded Systems (CASES) (HAMBURG, 18. September 2023 - 20. September 2023)

In: Proceedings of the International Conference on Compilers, Architectures, and Synthesis for Embedded Systems (CASES) 2023

BibTeX: Download

Kontakt

Dr.-Ing. Joachim Falk

- Telefon: +49 9131 85-25143

- E-Mail: joachim.falk@fau.de

Prof. Dr.-Ing. Jürgen Teich

- Telefon: +49 9131 85-25150

- E-Mail: juergen.teich@fau.de