# Domain-specific and Resource-aware Computing Frank Hannig

December, 2017

## Domain-specific and Resource-aware Computing

Domänenspezifisches und ressourcengewahres Rechnen

Der Technischen Fakultät der Friedrich-Alexander-Universität Erlangen-Nürnberg

als

## HABILITATIONSSCHRIFT

vorgelegt von

Dr.-Ing. Frank Hannig

Erlangen – 2017

Tag der Einreichung: 15. Dezember 2017 Erteilung der Lehrbefähigung (*venia legendi*): 11. Juli 2018

| Fachmentorat: | Professor DrIng. Jürgen Teich,<br>Friedrich-Alexander-Universität Erlangen-Nürnberg                        |

|---------------|------------------------------------------------------------------------------------------------------------|

|               | Professor DrIng. habil. Wolfgang Schröder-Preikschat,<br>Friedrich-Alexander-Universität Erlangen-Nürnberg |

|               | Professor DrIng. DrIng. habil. Robert Weigel,<br>Friedrich-Alexander-Universität Erlangen-Nürnberg         |

| Gutachter:    | Professor Paul H. J. Kelly,<br>Imperial College London                                                     |

|               | Professor Dr. rer. nat. Theo Ungerer,<br>Universität Augsburg                                              |

## Abstract

This cumulative habilitation treatise summarizes the research I have conducted with my group Architecture and Compiler Design (ACD) at the Chair of Hardware/Software Co-Design, focusing on selected results published within the last four years. My research can be divided mainly into two categories: *Resource-aware computing* and *domain-specific computing*. Both computing paradigms try to tackle the very complex programming and design challenge of parallel heterogeneous computer architectures, having different—to some extent common—goals in mind, e.g., performance, resource utilization, energy efficiency, predictability of even multiple execution qualities, or programming effort.

While resource-aware computing provides a full control loop from hardware status information to the program level and back, domain-specific computing drastically separates the concerns of algorithm development and target architecture implementation (including parallelization and low-level implementation details).

In the context of resource-aware computing, my research can be further subdivided into (1) modeling and system simulation and (2) architecture/compiler co-design of invasive tightly coupled processor arrays (TCPAs). In the area of domain-specific computing, three approaches are presented: (3) domain-specific high-level synthesis (HLS), (4) the heterogeneous image processing acceleration framework HIPAcc, and (5) the ExaStencils: Advanced stencil-code engineering approach.

## Contents

| 1 | Intr                                          | oductio                                                                                                           | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                          |

|---|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   | 1.1                                           | Contri                                                                                                            | ibutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3                                                                          |

|   | 1.2                                           | Papers                                                                                                            | s of this Habilitation Treatise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5                                                                          |

|   | 1.3                                           | Struct                                                                                                            | ure of this Habilitation Treatise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                                                          |

| 2 | Res                                           | ource-a                                                                                                           | ware Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                                                                          |

|   | 2.1                                           | Invasi                                                                                                            | ve Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                         |

|   | 2.2                                           | Model                                                                                                             | ing and System Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11                                                                         |

|   |                                               | 2.2.1                                                                                                             | Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11                                                                         |

|   |                                               | 2.2.2                                                                                                             | Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                                                                         |

|   |                                               | 2.2.3                                                                                                             | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13                                                                         |

|   |                                               | 2.2.4                                                                                                             | Key Papers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                                         |

|   | 2.3                                           | Archit                                                                                                            | ecture/Compiler Co-Design of Invasive TCPAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15                                                                         |

|   |                                               | 2.3.1                                                                                                             | Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15                                                                         |

|   |                                               | 2.3.2                                                                                                             | Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                         |

|   |                                               | 2.3.3                                                                                                             | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17                                                                         |

|   |                                               | 2.3.4                                                                                                             | Key Papers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18                                                                         |

| • | D                                             |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| 3 | Don                                           | nain-sp                                                                                                           | pecific Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23                                                                         |

| 3 | <b>Don</b><br>3.1                             | -                                                                                                                 | ecific Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>23</b><br>24                                                            |

| 3 |                                               | -                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| 3 |                                               | Doma                                                                                                              | in-specific Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24                                                                         |

| 3 |                                               | Doma<br>3.1.1<br>3.1.2                                                                                            | in-specific Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24<br>26                                                                   |

| 3 | 3.1                                           | Doma<br>3.1.1<br>3.1.2                                                                                            | in-specific Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24<br>26<br>27                                                             |

| 3 | 3.1                                           | Doma:<br>3.1.1<br>3.1.2<br>Doma:                                                                                  | in-specific Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24<br>26<br>27<br>29                                                       |

| 3 | 3.1                                           | Doma<br>3.1.1<br>3.1.2<br>Doma<br>3.2.1                                                                           | in-specific LanguagesDefinitionClassification of DSLsin-specific High-level SynthesisGoals for Domain-specific HLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24<br>26<br>27<br>29<br>30                                                 |

| 3 | 3.1                                           | Doma<br>3.1.1<br>3.1.2<br>Doma<br>3.2.1<br>3.2.2                                                                  | in-specific LanguagesDefinitionClassification of DSLsin-specific High-level SynthesisGoals for Domain-specific HLSApproach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24<br>26<br>27<br>29<br>30<br>31                                           |

| 3 | 3.1                                           | Doma<br>3.1.1<br>3.1.2<br>Doma<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                                | in-specific Languages       Definition         Definition       Classification of DSLs         classification of DSLs       Goals for Domain-specific HLS         Goals for Domain-specific HLS       Goals         Approach       Goals         Results       Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24<br>26<br>27<br>29<br>30<br>31<br>32                                     |

| 3 | 3.1<br>3.2                                    | Doma<br>3.1.1<br>3.1.2<br>Doma<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                                                | in-specific LanguagesDefinitionClassification of DSLsin-specific High-level SynthesisGoals for Domain-specific HLSApproachResultsDomain-specific HLS Key Papers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24<br>26<br>27<br>29<br>30<br>31<br>32<br>33                               |

| 3 | 3.1<br>3.2                                    | Doma<br>3.1.1<br>3.1.2<br>Doma<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>HIPAC                                       | in-specific Languages       Definition         Definition       Classification of DSLs         in-specific High-level Synthesis       Goals for Domain-specific HLS         Goals for Domain-specific HLS       Goals         Approach       Goals         Domain-specific HLS       Goals         Classification of DSLs       Goals         Goals for Domain-specific HLS       Goals         Classification of DSLs       Goals         Classification of DSLs       Goals         Goals for Domain-specific HLS       Goals         Classification of DSLs       Goals         Classification of DSLs       Goals         Goals for Domain-specific HLS       Goals         Classification of DSLs       Goals         Classificat | 24<br>26<br>27<br>29<br>30<br>31<br>32<br>33<br>34                         |

| 3 | 3.1<br>3.2                                    | Doma<br>3.1.1<br>3.1.2<br>Doma<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>HIPAC<br>3.3.1                              | in-specific LanguagesDefinitionClassification of DSLsclassification of DSLsin-specific High-level SynthesisGoals for Domain-specific HLSApproachResultsDomain-specific HLS Key Paperscc: The Heterogeneous Image Processing Acceleration FrameworkHIPAcc Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24<br>26<br>27<br>29<br>30<br>31<br>32<br>33<br>34<br>35                   |

| 3 | 3.1<br>3.2                                    | Doma<br>3.1.1<br>3.1.2<br>Doma<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>HIPAc<br>3.3.1<br>3.3.2                     | in-specific LanguagesDefinitionClassification of DSLsin-specific High-level SynthesisGoals for Domain-specific HLSApproachResultsDomain-specific HLS Key Papersc: The Heterogeneous Image Processing Acceleration FrameworkHIPAcc GoalsHIPAcc Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24<br>26<br>27<br>30<br>31<br>32<br>33<br>34<br>35<br>35                   |

| 3 | 3.1<br>3.2                                    | Doma:<br>3.1.1<br>3.1.2<br>Doma:<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>HIPAC<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4 | in-specific LanguagesDefinitionClassification of DSLsin-specific High-level SynthesisGoals for Domain-specific HLSApproachResultsDomain-specific HLS Key Paperscc: The Heterogeneous Image Processing Acceleration FrameworkHIPAcc GoalsHIPAcc ResultsHIPAcc Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24<br>26<br>27<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>35<br>35       |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Doma:<br>3.1.1<br>3.1.2<br>Doma:<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>HIPAC<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4 | in-specific LanguagesDefinitionClassification of DSLsin-specific High-level SynthesisGoals for Domain-specific HLSApproachResultsDomain-specific HLS Key PapersDomain-specific HLS Key Papersc: The Heterogeneous Image Processing Acceleration FrameworkHIPAcc GoalsHIPAcc ResultsHIPAcc ResultsHIPAcc Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24<br>26<br>27<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>35<br>37<br>38 |

|   |      | 3.4.3   | ExaStencils Results                                                                                                       | 44  |

|---|------|---------|---------------------------------------------------------------------------------------------------------------------------|-----|

|   |      | 3.4.4   | ExaStencils Key Papers                                                                                                    | 44  |

| 4 | Con  | clusior | 15                                                                                                                        | 47  |

| A | Bibl | iograpl | hy                                                                                                                        | 49  |

|   | A.1  | Genera  | al Bibliography                                                                                                           | 49  |

|   | A.2  |         | al Bibliography                                                                                                           | 60  |

| B | Ima  | ge Cred | lits                                                                                                                      | 81  |

| С | Pap  | er Repi | rints                                                                                                                     | 83  |

|   | C.1  | Resour  | rce-aware Computing                                                                                                       | 87  |

|   |      | C.1.1   | Modeling and System Simulation Papers                                                                                     | 87  |

|   |      |         | cations on Heterogeneous Tiled Architectures                                                                              | 87  |

|   |      |         | X10 '16: ActorX10: An Actor Library for X10                                                                               | 93  |

|   |      |         | ESTIMedia '17: High Performance Network-on-Chip Simulation                                                                |     |

|   |      |         | by Interval-based Timing Predictions                                                                                      | 99  |

|   |      | C.1.2   | Papers on Architecture/Compiler Co-Design of Invasive TCPAs<br>ACM TECS '14: Invasive Tightly-Coupled Processor Arrays: A | 109 |

|   |      |         | Domain-Specific Architecture/Compiler Co-Design                                                                           |     |

|   |      |         | Approach                                                                                                                  | 109 |

|   |      |         | Configurable Accelerators Using C++ Templates                                                                             | 139 |

|   |      |         | Springer JSPS '14: Symbolic Mapping of Loop Programs onto                                                                 | 157 |

|   |      |         | Processor Arrays                                                                                                          | 147 |

|   |      |         | MEMOCODE '14: Symbolic Inner Loop Parallelisation for Mas-                                                                |     |

|   |      |         | sively Parallel Processor Arrays                                                                                          | 177 |

|   |      |         | ACM TECS '17: Symbolic Multi-Level Loop Mapping of Loop                                                                   |     |

|   |      |         | Programs for Massively Parallel Processor Arrays                                                                          | 187 |

|   |      |         | ASAP '16: Modulo Scheduling of Symbolically Tiled Loops for                                                               |     |

|   |      |         | Tightly Coupled Processor Arrays                                                                                          | 215 |

|   |      |         | Springer JSPS '14: Compact Code Generation for Tightly-Coupled                                                            |     |

|   |      |         | Processor Arrays                                                                                                          | 225 |

|   | C.2  | Domai   | n-specific Computing                                                                                                      | 251 |

|   |      | C.2.1   | Domain-specific HLS Papers                                                                                                | 251 |

|   |      |         | ASAP '14: Domain-Specific Augmentations for High-Level Syn-                                                               |     |

|   |      |         | thesis                                                                                                                    | 251 |

|   |      |         | FPL '14: An Image Processing Library for C-based High-Level                                                               |     |

|   |      |         | Synthesis                                                                                                                 | 257 |

|       | Springer JSPS '17: A Novel Image Impulse Noise Removal Algo-  |     |

|-------|---------------------------------------------------------------|-----|

|       | rithm Optimized for Hardware Accelerators                     | 261 |

|       | ASAP '17: Hardware Design and Analysis of Efficient Loop      |     |

|       | Coarsening and Border Handling for Image Processing           | 279 |

| C.2.2 | HIPAcc Papers                                                 | 289 |

|       | IEEE TPDS '16: HIPAcc: A Domain-Specific Language and Com-    |     |

|       | piler for Image Processing                                    | 289 |

|       | DATE '14: Code Generation for Embedded Heterogeneous Ar-      |     |

|       | chitectures on Android                                        | 305 |

|       | CODES+ISSS '14: Code Generation from a Domain-specific Lan-   |     |

|       | guage for C-based HLS of Hardware Accelerators                | 311 |

|       | Elsevier JPDC '14: Towards a Performance-portable Description |     |

|       | of Geometric Multigrid Algorithms using a Domain-             |     |

|       | specific Language                                             | 321 |

|       | FPL '16: FPGA-based Accelerator Design from a Domain-Specific |     |

|       | Language                                                      | 333 |

|       | Springer JSPS '17: Loop Parallelization Techniques for FPGA   |     |

|       | Accelerator Synthesis                                         | 343 |

|       | LCTES '17: Auto-vectorization for Image Processing DSLs       | 369 |

| C.2.3 | ExaStencils Papers                                            | 379 |

|       | ICCSA '14: An Evaluation of Domain-Specific Language Tech-    |     |

|       | nologies for Code Generation                                  | 379 |

|       | Euro-Par '14: ExaStencils: Advanced Stencil-Code Engineering  | 389 |

|       | WOLFHPC '14: ExaSlang: A Domain-Specific Language for         |     |

|       | Highly Scalable Multigrid Solvers                             | 401 |

|       | Springer LNCSE '16: Systems of Partial Differential Equations |     |

|       | in ExaSlang                                                   | 411 |

## List of Abbreviations

| ACD   | Architecture and Compiler Design                |

|-------|-------------------------------------------------|

| ADAS  | Advanced Driver Assistance System               |

| ALU   | Arithmetic Logic Unit                           |

| APGAS | Asynchronously Partitioned Global Address Space |

| ASIC  | Application-Specific Integrated Circuit         |

| ASIP  | Application-Specific Instruction set Processor  |

| AST   | Abstract Syntax Tree                            |

| AVX   | Advanced Vector Extensions                      |

| BRAM  | Block Random Access Memory                      |

| CGRA  | Coarse-Grained Reconfigurable Architecture      |

| CMOS  | Complementary Metal Oxide Semiconductor         |

| CNC   | Computer Numerical Control                      |

| CPU   | Central Processing Unit                         |

| DAG   | Directed Acyclic Graph                          |

| DLP   | Data-Level Parallelism                          |

| DoP   | Degree of Parallelism                           |

| DSL   | Domain-Specific programming Language            |

| DSP   | Digital Signal Processor                        |

| FLOPS | FLoating-point Operations Per Second            |

| FPGA  | Field Programmable Gate Array                   |

| FU    | Functional Unit                                 |

| GPU   | Graphics Processing Unit                        |

|       |                                                 |

#### LIST OF ABBREVIATIONS

| HDL    | Hardware Description Language         |

|--------|---------------------------------------|

| HLS    | High-Level Synthesis                  |

| HPC    | High-Performance Computing            |

| HSA    | Heterogeneous System Architecture     |

| IC     | Integrated Circuit                    |

| ILP    | Instruction-Level Parallelism         |

| IR     | Intermediate Representation           |

| LoC    | Lines of Code                         |

| LPGS   | Locally Parallel, Globally Sequential |

| LSGP   | Locally Sequential, Globally Parallel |

| LUT    | Look-Up Table                         |

| MIPS   | Million Instructions Per Second       |

| MPI    | Message Passing Interface             |

| MPSoC  | Multi-Processor System-on-Chip        |

| NoC    | Network-on-Chip                       |

| NPP    | Nvidia Performance Primitives         |

| OpenCL | Open Computing Language               |

| OpenCV | Open Source Computer Vision           |

| РС     | Personal Computer                     |

| PDE    | Partial Differential Equation         |

| PE     | Processing Element                    |

| QoR    | Quality of Results                    |

| RISC   | Reduced Instruction Set Computer      |

| SDK    | Software Development Kit              |

| SIMD   | Single Instruction, Multiple Data     |

| SNR   | Signal-to-Noise Ratio                |

|-------|--------------------------------------|

| SoC   | System-on-Chip                       |

| SQL   | Structured Query Language            |

| SSE   | Streaming SIMD Extensions            |

| ТСРА  | Tightly Coupled Processor Array      |

| TI    | Texas Instruments                    |

| TPDL  | Target Platform Description Language |

| UML   | Unified Modeling Language            |

| VHDL  | VHSIC Hardware Description Language  |

| VHLL  | Very High-Level programming Language |

| VHSIC | Very High Speed IC                   |

| VLIW  | Very Long Instruction Word           |

## 1 Introduction

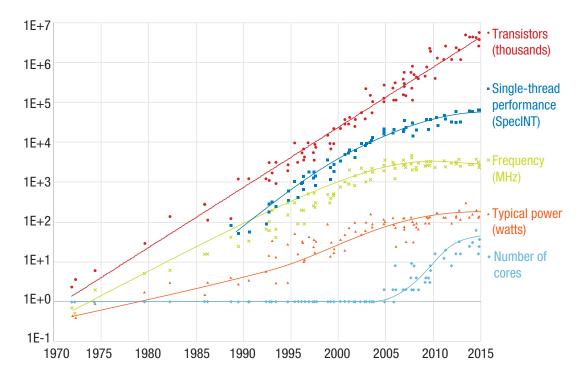

Diversity accompanies electronics ab initio. First electronic devices were assembled from discrete components to fulfill a particular purpose, i.e., they were designed and implemented in an application-specific way. Quickly, more and more transistors, the basis for all logic gates and registers, could be crammed onto integrated circuits and offered an almost unlimited plethora of possibilities for digital circuits. Thanks to the steady advances in Complementary Metal Oxide Semiconductor (CMOS) technology, the number of transistors on the same chip footprint has grown exponentially within the last half-century. This observation/projection is widely known as Moore's law [107] and goes along with Dennard scaling [32], which roughly says that the power density remains constant as transistors are getting smaller, i.e., performance per watt is also growing exponentially. In the context of microprocessors, Central Processing Unit (CPU) designers harnessed this growth 30 years long by turning it into performance gains. First, because not only more transistors but also faster transistors have been built, and thus even CPUs could run increasingly at higher clock rates. Second, ever more complex CPUs could be designed that can do more work per clock cycle. That is, more powerful instructions and larger data types, deeper processor pipelines, sophisticated branch prediction, multiple parallel instructions, or instruction reordering in the case of out-oforder execution. A third performance boost has been accomplished thanks to larger and hierarchically organized caches. However, the seemingly never-ending performance boost of single-core processors was disrupted around 2005. Herb Sutter described this turning point in microprocessor history in his highly cited article "A Fundamental Turn Toward Concurrency in Software" [134] and the 2009 updated version "The Free Lunch is Over" [135], respectively. Herein, Sutter states that there is almost no progress in achieving higher clock frequencies. Although single transistors and small Integrated Circuits (ICs) have been experimentally proven to run at frequencies in the two-digit to three-digit gigahertz (GHz) range, processor clock rates have nearly saturated due to several physical effects. (a) Shrinking features sizes came along with severe current leakage<sup>1</sup> issues, (b) the power consumption is limited, and the two items as mentioned above lead to (c) profound heat problems, in other words, heat is hard to dissipate. Collectively, these issues are referred to as the *power wall*. In addition, support for instruction level parallelism cannot be arbitrarily scaled within a processor core because increasing the number of functional units gets quickly exceedingly complex for both superscalar and Very Long Instruction Word (VLIW) processors [30]. All these threats

<sup>&</sup>lt;sup>1</sup>Leakage in semiconductor devices denotes the effect of capacity-connected components, such as transistors or diodes, to draw a small amount of current even though they are switched off.

Figure 1.1: Evolution of microprocessors with respect to (i) number of transistors per chip, (ii) benchmarked performance, (iii) clock rate, (iv) typical power consumption, and (v) number of processor cores. Figure reprinted from [23, p. 46]. © 2015 by IEEE.

induced the end of Dennard scaling in 2005 and turned processor architectures into multicore designs henceforward (see Figure 1.1).

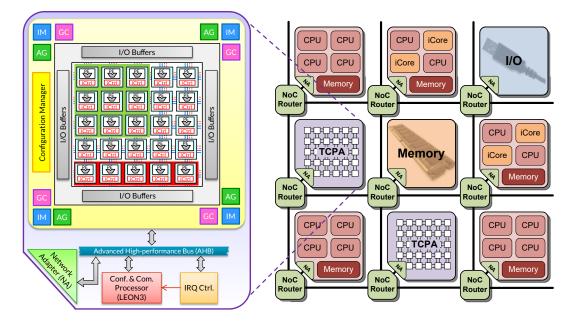

While the speed of Moore's projection has slightly slowed down, the steady miniaturization of feature sizes and the associated exponential growth of processor designs is still ongoing. However, as mentioned above, technology shrinking also continuously leads to higher energy densities, and thus the situation has become even more severe concerning power consumption because chips can handle only a limited power budget. As a consequence, the potentially available chip area might not be entirely utilized or at least not simultaneously. This phenomenon is also known as *utilization wall* [45] and accordingly as *dark silicon* [35], which denotes chip areas that must remain inactive most of the time. As a conclusion: Future systems will only scale if their energy efficiency will considerably improve—this reasoning holds for both embedded and portable devices, such as smartphones and tablets as well as large-scale systems used for High-Performance Computing (HPC). *Customization* and *heterogeneity*, e.g., in the form of custom-tailored memory hierarchies, sophisticated interconnection networks, and application-specific compute components, such as accelerators, are the key to success for future performance gains [127, 91]. Additionally, each CMOS process shrink is progressively ridden with imperfections (i.e., variability [14, 6]) and unreliability of the devices. These technological hurdles combined with the sheer complexity of heterogeneous Multi-Processor System-on-Chip (MPSoC) architectures raise numerous questions on how to design, test, and program such systems while having multiple—possibly contrary—goals in mind. It is very challenging to find solutions satisfying different objectives, such as performance, resource utilization, energy efficiency, resiliency [69], predictability of even multiple execution qualities [140], effective exploitation of concurrency, or programming effort. Thus, novel design methodologies and computing paradigms are required to fuel research and scientific discoveries with undiminished pace.

### 1.1 Contributions

In recent years, my research mission has been to master the design and programming complexity of parallel systems as well as their rising heterogeneity. The considered systems span a wide range, from architectures targeted for embedded applications to clusters for HPC. A particular focus is on accelerators (e.g., processor arrays, Graphics Processing Units (GPUs), or dedicated hardware implemented in Field Programmable Gate Arrays (FPGAs)) or their combination as part of a heterogeneous system (e.g., compute nodes equipped with accelerator technology, MPSoCs, or NoC-based tiled heterogeneous architectures). Investigated are programming languages, methods and techniques for compilation and application mapping, as well as the synthesis and simulation of parallel processor architectures. Here, two strategic approaches are researched-which may appear utterly different at first. The one is *resource-aware computing*, and the other is *domain-specific computing*. While the former makes numerous static architecture properties as well as runtime status information explicitly visible (e.g., at the program level as in the case of *resource-aware programming* [139, 142, P69]), the latter tries to wholly separate application development from an underlying architecture (i.e., a programmer is shielded from low-level implementation, mapping and parallelization details). Concerning these two computing paradigms, my principal research contributions can be very briefly summarized as follows:

#### **Resource-aware Computing**

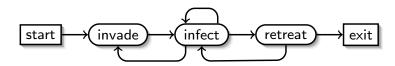

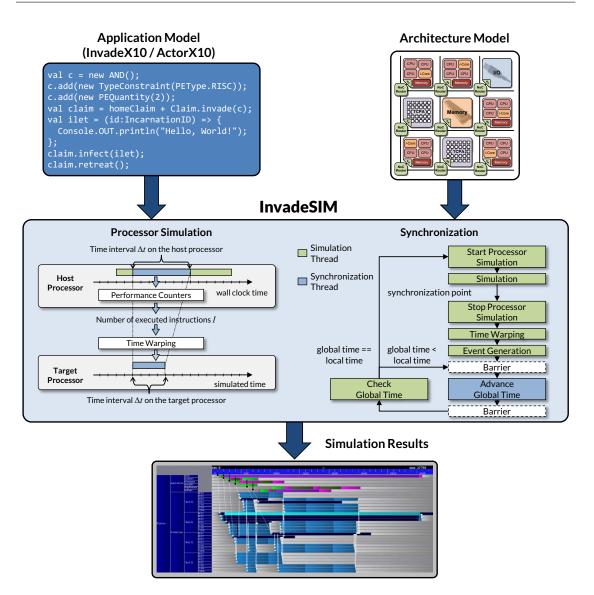

(1) Modeling and System Simulation. Invasive computing [139, 142] is resourceaware computing at its best. To study resource-aware programming [139, P69] and *invasive* resource management strategies [68], means for application modeling and to mimic the execution behavior on not yet existing manycore architectures are required. The modeling of *invasive* applications includes programming extensions for resource-aware programming [P69] as well as concurrent models of computation, such as *actor models* [P42, P16**2**]. Timed functional simulation techniques [P65, P24**2**] are used to assess execution qualities and to explore variants [P62] of tiled heterogeneous manycore architectures. Measures for fast full system simulation (parallel simulation [P24**2**] and Network-on-Chip (NoC) simulation [P47, P4**2**]) have been investigated and evaluated for streaming-based multimedia applications [P16**2**] as well as X10 benchmarks [P24**2**].

(2) Architecture/Compiler Co-Design of Invasive TCPAs. Invasive Tightly Coupled Processor Arrays (TCPAs) [J18<sup>■</sup>] combine architectural research in the field of parallel on-chip accelerators with the paradigm of invasive computing. The concepts to dynamically *invade* processors and to *retreat* from them are directly integrated into an invasive TCPA at the hardware level [P71, P67, J18<sup>■</sup>]. This opens opportunities for ultrafast resource reservation and adaptivity (e.g., power management [J19, J18<sup>■</sup>] or fault tolerance [P23, P21, 84]). These techniques have been mainly evaluated using cycle-accurate simulation [P101, J18<sup>■</sup>, P5<sup>■</sup>].

Regarding compilation for TCPAs, (a) efficient, yet *compact code generation* [P46, J17**2**] as well as (b) *symbolic tiling* and *symbolic scheduling* [P48, J15**2**, P32**2**, P19, P15**2**, J1**2**] as program transformations for the symbolic parallelization of nested loop programs with uniform data dependences have been investigated.

#### **Domain-specific Computing**

- (3) Domain-specific High-level Synthesis. Domain-specific High-Level Synthesis (HLS) provides programming abstractions to ease the problem specification and thus productivity. In the case of this habilitation treatise, the domain is image processing. The considered techniques are based on *template metaprogramming* and *generative programming*. The proposed domain-specific concepts have been investigated employing external Domain-Specific programming Language (DSL) constructs followed by code transformations in the case of the PARO HLS research tool [P37<sup>a</sup>, J2<sup>a</sup>] and the form of a template library in the case of C-based commercial tools, such as Xilinx Vivado HLS [P33<sup>a</sup>, P9<sup>a</sup>].

- (4) The Heterogeneous Image Processing Acceleration Framework. HIPAcc is a DSL embedded in C++ and a compiler framework for the domain of image processing. It captures domain knowledge in a compact and intuitive language and employs source-to-source translation combined with various optimizations to achieve an excellent productivity paired with performance portability. The HIPAcc approach has been applied and evaluated for a broad variety of parallel accelerator architectures, including manycore processors [J9<sup>2</sup>, J12<sup>2</sup>], such as Nvidia and AMD GPUs and Intel Xeon Phi, embedded GPUs [P41<sup>2</sup>], Xilinx and Intel/Altera FPGAs [P31<sup>2</sup>, P13<sup>2</sup>], J5<sup>2</sup>], and vector units [P11<sup>2</sup>].

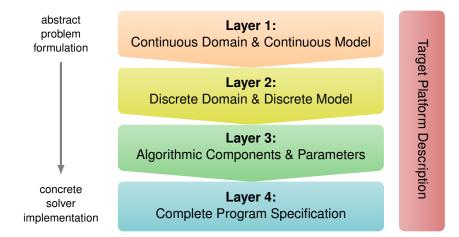

(5) The ExaStencils Approach. To reduce the foreseen performance/productivity gap of upcoming exascale platforms, a unique, tool-assisted co-design approach specific for the domain of multigrid methods based on stencil computations is developed within ExaStencils [P35<sup>■</sup>, P38<sup>■</sup>]. The fundamental concept of ExaStencils is a multi-layered external DSL in combination with a modular transformation and optimization framework [P29<sup>■</sup>]. The approach has been evaluated concerning productivity and scalability, among other things, for a generated geometric multigrid solver on the JUQUEEN supercomputer [C1<sup>■</sup>].

I have conducted the in this habilitation treatise cumulated research jointly together with nine doctoral researchers as well as bachelor and master students from my research group *Architecture and Compiler Design (ACD)*.<sup>2</sup> I have been the principal investigator for (1), (4), and (5) within the DFG Transregional Collaborative Research Centre 89 "Invasive Computing," the DFG Research Training Group 1773 "Heterogeneous Image Systems," and the DFG Priority Programme 1648 "Software for Exascale Computing," respectively. In the case of (2), I have been a conceptual contributor, and in the case of (3), I have been the scientific leader and conceptual contributor.

### 1.2 Papers of this Habilitation Treatise

This document is a cumulative habilitation treatise. From my 165 peer-reviewed publications listed in Appendix A.2 (page 60ff.), I have opted for the following 25 key contributions of my research. These form the chief part of my cumulative habilitation treatise. The full texts (i.e., reprints) of these publications are provided on page 83ff. in Appendix C.

### **Resource-aware Computing**

#### **Modeling and System Simulation Papers**

| DAC '15<br>page 87ff.              | Roloff, Schafhauser, Hannig, and Teich. "Execution-driven parallel simulation of PGAS applications on heterogeneous tiled architectures" | [P24 <b>/</b> ] |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <b>X10 '16</b><br>page 93ff.       | Roloff, Pöppl, Schwarzer, Wildermann, Bader, Glaß, Hannig, and Teich. "Ac-<br>torX10: An actor library for X10"                          | [P16 <b>2</b> ] |

| <b>ESTIMedia '17</b><br>page 99ff. | Roloff, Hannig, and Teich. "High performance network-on-chip simulation by interval-based timing predictions"                            | [P4 <b>@</b> ]  |

<sup>&</sup>lt;sup>2</sup>In November 2017, my team, the ACD group, consists of eleven doctoral researchers and one post-doctoral researcher.

## Papers on Architecture/Compiler Co-Design of Invasive TCPAs

| ACM TECS '14 page 109ff.             | Hannig, Lari, Boppu, Tanase, and Reiche. "Invasive tightly-coupled processor arrays: A domain-specific architecture/compiler co-design approach" | [J18 <b>@</b> ] |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <b>RSP '17</b><br>page 139ff.        | Witterauf, Hannig, and Teich. "Constructing fast and cycle-accurate simulators for configurable accelerators using C++ templates"                | [P5 <b>/</b> ]  |

| <b>Springer JSPS '14</b> page 147ff. | Teich, Tanase, and Hannig. "Symbolic mapping of loop programs onto processor<br>arrays"                                                          | [J15 <b>@</b> ] |

| MEMOCODE '14 page 177ff.             | Tanase, Witterauf, Teich, and Hannig. "Symbolic inner loop parallelisation for massively parallel processor arrays"                              | [P32 <b>/</b> ] |

| ACM TECS '17<br>page 187ff.          | Tanase, Witterauf, Teich, and Hannig. "Symbolic multi-level loop mapping of loop programs for massively parallel processor arrays"               | [J1 <b>@</b> ]  |

| <b>ASAP '16</b><br>page 215ff.       | Witterauf, Tanase, Hannig, and Teich. "Modulo scheduling of symbolically tiled loops for tightly coupled processor arrays"                       | [P15 <b>@</b> ] |

| <b>Springer JSPS '14</b> page 225ff. | Boppu, Hannig, and Teich. "Compact code generation for tightly-coupled pro-<br>cessor arrays"                                                    | [J17 <b>/</b> ] |

## **Domain-specific Computing**

#### **Domain-specific HLS Papers**

| <b>ASAP '14</b><br>page 251ff.       | Schmid, Tanase, Hannig, Teich, Bhadouria, and Ghoshal. "Domain-specific aug-<br>mentations for high-level synthesis"                            | [P37 <b>/</b> ] |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <b>FPL '14</b><br>page 257ff.        | Schmid, Apelt, Hannig, and Teich. "An image processing library for C-based high-level synthesis"                                                | [P33 <b>@</b> ] |

| <b>Springer JSPS '17</b> page 261ff. | Bhadouria, Tanase, Schmid, Hannig, Teich, and Ghoshal. "A novel image im-<br>pulse noise removal algorithm optimized for hardware accelerators" | [J2 <b>@</b> ]  |

| <b>ASAP '17</b><br>page 279ff.       | Özkan, Reiche, Hannig, and Teich. "Hardware design and analysis of efficient<br>loop coarsening and border handling for image processing"       | [P9 <b>#</b> ]  |

### **HIPAcc Papers**

| IEEE TPDS '16<br>page 289ff.     | Membarth, Reiche, Hannig, Teich, Körner, and Eckert. "HIPAcc: A domain-<br>specific language and compiler for image processing"                                                 | [J9 <b>@</b> ]  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| DATE '14<br>page 305ff.          | Membarth, Reiche, Hannig, and Teich. "Code generation for embedded hetero-<br>geneous architectures on Android"                                                                 | [P41 <b>2</b> ] |

| CODES+ISSS '14<br>page 311ff.    | Reiche, Schmid, Hannig, Membarth, and Teich. "Code generation from a domain-specific language for C-based HLS of hardware accelerators"                                         | [P31 <b>2</b> ] |

| Elsevier JPDC '14 page 321ff.    | Membarth, Reiche, Schmitt, Hannig, Teich, Stürmer, and Köstler. "Towards a performance-portable description of geometric multigrid algorithms using a domain-specific language" | [J12 <b>@</b> ] |

| FPL '16<br>page 333ff.           | Özkan, Reiche, Hannig, and Teich. "FPGA-based accelerator design from a domain-specific language"                                                                               | [P13 <b>2</b> ] |

| Springer JSPS '17<br>page 343ff. | Reiche, Özkan, Hannig, Teich, and Schmid. "Loop parallelization techniques for<br>FPGA accelerator synthesis"                                                                   | [J5 <b>@</b> ]  |

| <b>LCTES '17</b><br>page 369ff.  | Reiche, Kobylko, Hannig, and Teich. "Auto-vectorization for image processing DSLs"                                                                                              | [P11 <b>2</b> ] |

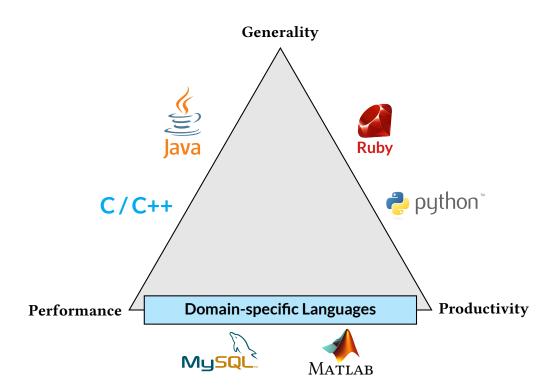

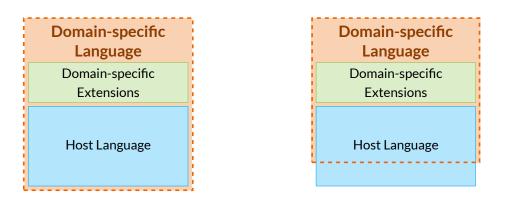

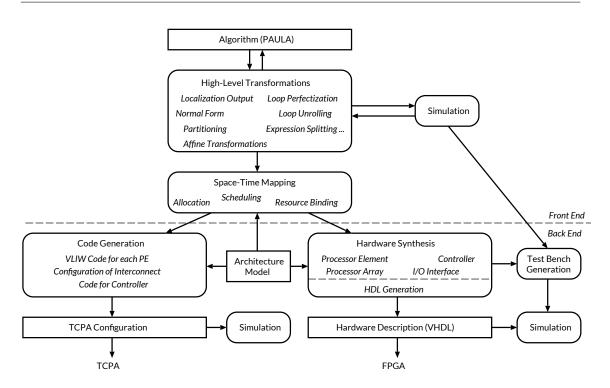

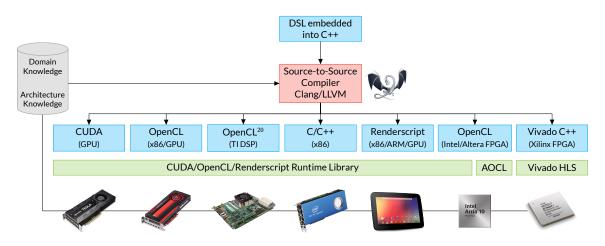

## **ExaStencils Papers**