# Scheduling Techniques for High-Throughput Loop Accelerators

Frank Hannig

#### Cite thesis as:

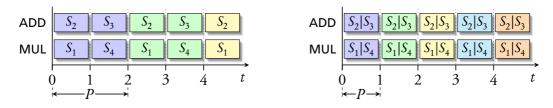

Frank Hannig. Scheduling Techniques for High-Throughput Loop Accelerators. Dissertation, University of Erlangen-Nuremberg, Germany, August 2009. Verlag Dr. Hut, Munich, Germany.

#### BibTeX:

```

@PHDTHESIS{Han09,

AUTHOR = {{Hannig}, {Frank}},

MONTH = aug,

NOTE = {Verlag Dr. Hut, Munich, Germany},

SCHOOL = {University of Erlangen-Nuremberg, Germany},

TITLE = {{Scheduling} {Techniques} for {High-Throughput} {Loop} {Accelerators}},

TYPE = {Dissertation},

YEAR = {2009},

ISSN_ISBN = {978-3-86853-220-3}

}

```

# Scheduling Techniques for High-Throughput Loop Accelerators

Der Technischen Fakultät der Universität Erlangen-Nürnberg zur Erlangung des Grades

D O K T O R - I N G E N I E U R

vorgelegt von

Frank Hannig

Erlangen – 2009

Als Dissertation genehmigt von der Technischen Fakultät der Universität Erlangen-Nürnberg

| Tag der Einreichung: | 8. Juni 2009                           |

|----------------------|----------------------------------------|

| Tag der Promotion:   | 11. August 2009                        |

| Dekan:               | Professor DrIng. habil. Johannes Huber |

| Berichterstatter:    | Professor DrIng. Jürgen Teich          |

|                      | Professor Dr. Krzysztof Kuchcinski     |

*This thesis is dedicated to my scintillating wife Ulrike with love and gratitude.*

## Acknowledgments

I would like to thank first and foremost my doctoral adviser, Professor Dr.-Ing. Jürgen Teich, for all the support and advice, his confidence, and the numerous and varied responsibilities he has given over the last years to me. I would also like to thank Professor Krzysztof Kuchcinski for being the co-examiner of my thesis.

I would like to thank everyone in the architecture and compiler design (ACD) group for interest, advice, and support. In no particular order they are Hritam Dutta, Dmitrij Kissler, Vahid Lari, Farhadur Arifin, Richard Membarth, Moritz Schmid, Sunil Shukla, and the former members Alexej Kupriyanov and Holger Ruckdeschel. Especially, I would like to thank Hritam for all the scientific discussions and friendly chats. Moreover, I truly appreciate the work of all the students who designed and implemented parts of the PARO high-level synthesis tool, especially Jiali Teddy Zhai.

I would like particularly thank my previous office mate and office neighbor, respectively, Christian Haubelt for all the discussions concerning all issues of the chair of Hardware/Software Co-Design. I would like to thank Dirk Koch for his helpfulness, especially for his valuable knowledge in hardware design, the chats and sharing food with him at nights and weekends when finalizing this thesis.

I would like to thank Hritam and Moritz who took the time to read over my thesis and providing very valuable feedback.

Last, and by no means least, thanks to my family. I would like to thank my parents for my technical-oriented advancement, their constant support, and interest in my work as long as I got my first Lego bricks from them. Finally, I would like to thank my children Ricarda Sophie and Constantin Leander, and my wife Ulrike for their support, endless patience, and love.

Frank Hannig Erlangen, August 2009

# Contents

| Ac         | knov         | vledgmo | nts                          |                                       | v  |

|------------|--------------|---------|------------------------------|---------------------------------------|----|

| 1          | Introduction |         |                              |                                       | 1  |

|            | 1.1          | Contri  | outions and Bibliographic No | otes                                  | 8  |

|            | 1.2          |         | <b>U</b>                     |                                       | 12 |

| 2 Modeling |              |         |                              | 13                                    |    |

|            | 2.1          | •       | red Computations and Algor   | ithm Classes in the Polytope Model    | 14 |

|            |              | 2.1.1   |                              | · · · · · · · · · · · · · · · · · · · | 15 |

|            |              | 2.1.2   |                              | egular Algorithms                     | 19 |

|            |              | 2.1.3   | •                            |                                       | 21 |

|            |              | 2.1.4   |                              |                                       | 22 |

|            | 2.2          | Langu   |                              |                                       | 26 |

|            |              | 2.2.1   |                              | · · · · · · · · · · · · · · · · · · · | 26 |

|            |              |         |                              | ctional Programming and Loop-         |    |

|            |              |         |                              | 6 6 1                                 | 28 |

|            |              |         |                              |                                       | 29 |

|            |              |         | e e                          | 6 6                                   | 29 |

|            |              |         |                              | ng Languages                          | 31 |

|            |              | 2.2.2   |                              |                                       | 31 |

|            |              |         |                              | tion                                  | 31 |

|            |              |         |                              |                                       | 41 |

|            | 2.3          | Summ    |                              | •                                     | 45 |

| 3          | Sche         | eduling | and Allocation               |                                       | 47 |

|            | 3.1          | U       |                              |                                       | 48 |

|            |              | 3.1.1   |                              |                                       | 48 |

|            |              | -       |                              | ••••••••••••••••••                    | 51 |

|            |              | _       |                              |                                       | 52 |

|            |              |         | e                            | 1                                     | 53 |

|            |              |         | 0                            |                                       |    |

|                            |                           |                        | 3.1.2.3     | Scheduling of Loop Programs and Loop Paralleliza-    |     |

|----------------------------|---------------------------|------------------------|-------------|------------------------------------------------------|-----|

|                            |                           |                        |             | tion                                                 | 54  |

|                            |                           | 3.1.3                  | Differen    | tiation                                              | 57  |

|                            | 3.2                       | Prelim                 | inaries     |                                                      | 58  |

|                            | 3.3                       | Allocat                | tion and S  | Space Mapping                                        | 59  |

|                            |                           | 3.3.1                  |             | n                                                    | 62  |

|                            |                           | 3.3.2                  |             | ing                                                  | 63  |

|                            |                           | 3.3.3                  |             | ical Partitioning                                    | 66  |

|                            | 3.4                       | Linear                 | Scheduli    | ng                                                   | 69  |

|                            | 3.5                       |                        |             | ng                                                   | 71  |

|                            |                           | 3.5.1                  |             | cheduling with Projection as Allocation              | 74  |

|                            |                           |                        | 3.5.1.1     | Determination of the Iteration Interval              | 74  |

|                            |                           |                        | 3.5.1.2     | Linearly Bounded Lattice as Iteration Space          | 77  |

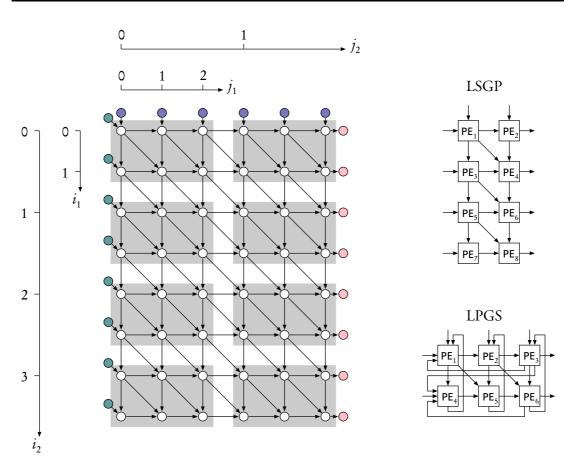

|                            |                           | 3.5.2                  | Affine So   | cheduling with Partitioning as Allocation            | 79  |

|                            |                           |                        | 3.5.2.1     | Determination of Strides and Path Strides            | 79  |

|                            |                           |                        | 3.5.2.2     | Sequentialization Constraint                         | 93  |

|                            |                           |                        | 3.5.2.3     | Mixed Integer Program for LSGP and LPGS Parti-       |     |

|                            |                           |                        |             | tioned Algorithms                                    | 93  |

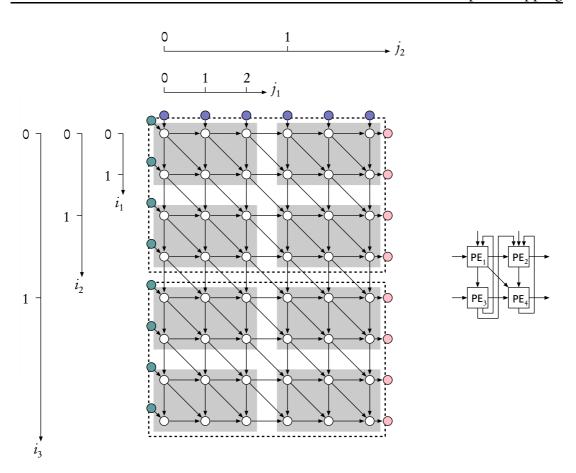

|                            |                           |                        | 3.5.2.4     | Mixed Integer Program for Hierarchically Partitioned |     |

|                            |                           |                        |             | Algorithms                                           | 96  |

|                            |                           |                        | 3.5.2.5     | On the Number of Sequentialization Orders            | 97  |

|                            |                           | 3.5.3                  | Allocatio   | on of Resources within Processors                    | 100 |

|                            |                           |                        | 3.5.3.1     | Resource Constraints                                 | 101 |

|                            |                           |                        | 3.5.3.2     | Remarks                                              | 105 |

|                            | 3.6                       | Conditional Scheduling |             | 106                                                  |     |

|                            |                           | 3.6.1                  | AND-X       | OR-Tree                                              | 112 |

|                            |                           | 3.6.2                  | Resource    | e Constraints for Conditional Execution              | 116 |

|                            | 3.7 Lifetime of Variables |                        | ables       | 122                                                  |     |

| 3.7.1 Lifetime Constraints |                           | Constraints            | 124         |                                                      |     |

|                            | 3.8                       | Schedu                 | uling for V | Weakly-Programmable Processor Arrays                 | 125 |

|                            |                           | 3.8.1                  | Weakly-     | Programmable Processor Arrays                        | 125 |

|                            |                           | 3.8.2                  | Register    | Constraints                                          | 127 |

|                            |                           | 3.8.3                  | Channel     | Constraints                                          | 133 |

|                            | 3.9                       | Summ                   | ary         |                                                      | 142 |

| 4                          | Targ                      | et Cod                 | e Generat   | tion                                                 | 143 |

|                            |                           |                        |             |                                                      | 144 |

|                            |                           | 4.1.1                  | High-Le     | vel Synthesis Approaches and Tools                   | 144 |

|                            |                           |                        | 4.1.1.1     |                                                      |     |

|   |      | 4.1.1.2 Tools and Approaches for the Acceleration of Loop<br>Programs            |

|---|------|----------------------------------------------------------------------------------|

|   |      | 4.1.1.3 High-Level Synthesis Tools and Approaches based<br>on C, C++, or SystemC |

|   |      | 4.1.2 Mapping Approaches for Coarse-Grained and Embedded Multi-                  |

|   |      | Processor Arrays                                                                 |

|   |      | 4.1.3 Unified Approaches                                                         |

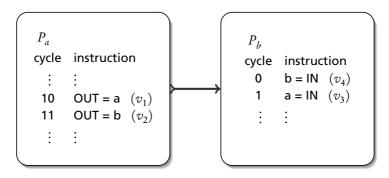

|   | 4.2  | The PARO Synthesis Tool                                                          |

|   | 4.3  | Synthesis of Dedicated Hardware Accelerators                                     |

|   | 110  | 4.3.1 Classification of Processor Elements                                       |

|   |      | 4.3.2 Synthesis of Interconnection Structure                                     |

|   |      | 4.3.3 Synthesis of Processor Elements                                            |

|   |      | 4.3.4 Synthesis of Control Structure                                             |

|   | 4.4  | Code Generation for Weakly-Programmable Processor Arrays 158                     |

|   |      | 4.4.1 Mapping Flow                                                               |

|   | 4.5  | Summary and Conclusions                                                          |

| 5 | Exp  | eriments and Evaluation 163                                                      |

| - | 5.1  | Sequentialized Scheduling 163                                                    |

|   | 5.2  | Predicated and Conditional Execution                                             |

|   | 5.3  | Scheduling with Register Constraints 175                                         |

|   | 5.4  | Scheduling for WPPA 176                                                          |

|   | 5.5  | High-Level Synthesis for FPGA Targets                                            |

|   | 5.6  | Loop Unrolling versus Loop Partitioning                                          |

|   | 5.7  | Real World Case Study 194                                                        |

|   | 5.8  | Summary 198                                                                      |

| 6 | Con  | clusions and Future Work 201                                                     |

|   | 6.1  | Summary                                                                          |

|   | 6.2  | Future Work Directions                                                           |

| A | Line | ear Programming 205                                                              |

|   | A.1  | Linear Programming in a Nutshell 205                                             |

|   | A.2  | Formulation of Maximum-Constraints 207                                           |

|   |      | A.2.1 Modification of the Objective Function                                     |

|   |      | A.2.2 Usage of Binary Variables                                                  |

| B | Furt | her Details of the PAULA Language 209                                            |

|   |      | Lexical Structure                                                                |

|   |      | B.1.1 White Space                                                                |

|   |      |                                                                                  |

|         | B.1.2   | Commen     | nts                        | . 209 |

|---------|---------|------------|----------------------------|-------|

|         | B.1.3   | Tokens .   |                            | . 210 |

|         |         | B.1.3.1    | Words                      | . 210 |

|         |         | B.1.3.2    | String Literals            | . 210 |

|         |         | B.1.3.3    | Integer and Float Literals | . 210 |

|         |         | B.1.3.4    | Boolean Literals           | . 211 |

|         |         | B.1.3.5    | Special Tokens             | . 211 |

|         | B.1.4   | Inclusion  | of other Files             | . 211 |

|         | B.1.5   | Special St | tatements                  | . 211 |

| B.2     | Data 7  | Гурев      |                            | . 212 |

|         | B.2.1   | Built-in I | Data Types                 | . 212 |

|         |         | B.2.1.1    | notype                     | . 212 |

|         |         | B.2.1.2    | boolean                    | . 212 |

|         |         | B.2.1.3    | integer                    | . 212 |

|         |         | B.2.1.4    | fixed                      | . 212 |

|         |         | B.2.1.5    | float                      |       |

|         | B.2.2   | Туре Со    | nversions                  |       |

|         |         | B.2.2.1    | Automatic Conversions      |       |

|         | B.2.3   | -          | Conversions                |       |

| B.3     |         | •          | ds                         |       |

| B.4     |         |            | haracter Operators         |       |

| B.5     | EBNF    | of PAUL    | A                          | . 218 |

| German  | Dart    |            |                            | 221   |

|         |         | 2551100    |                            |       |

| 2436    |         |            |                            | •     |

| Bibliog | raphy   |            |                            | 227   |

| Acrony  | ms      |            |                            | 279   |

| Curricu | ılum Vi | tae        |                            | 283   |

| Author  | 's Own  | Publicatio | ons                        | 285   |

# Chapter 1

# Introduction

The desire for more mobility and the enthusiasm for ubiquitous electronic gadgets on the one hand side and the steady progress in semiconductor industry on the other hand are the driving forces in the market of embedded digital systems. The growing number of stream-based applications is eager for more computational power. Examples of such systems include handhelds for digital audio and video broadcasting and navigation, next generation game and entertainment consoles with high-definition television (HDTV) support and high-capacity storage media like HD DVD or Bluray Disc. Other demanding applications with real-time requirements can be found in the areas of medical image processing, radar technology, and robotics.

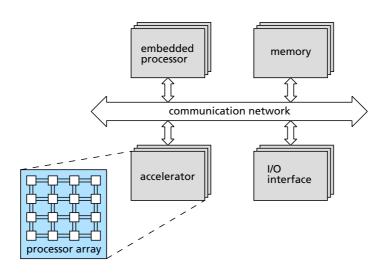

Feature sizes reaching nanoscopic scale allow implementations of complex systems on a single die. These designs are called *system-on-a-chip* (SoC) or in case multiple embedded processors are included, *multiprocessor system-on-a-chip* (MPSoC). The usual components of such a system are sketched in Figure 1.1. Typically, an SoC consists of one or more embedded processors, memories, I/O interfaces, accelerators for dedicated tasks, and a communication network for connecting the individual parts of the system. Note that the communication network as indicated by the graphic can be an arbitrary, maybe hierarchic interconnect structure, which might consist of several busses or point-to-point connections. The situation for the accelerators is similar. Here, an abundance of variations exists, ranging from custom hardware in form of application-specific integrated circuits (ASICs) to fine-grained reconfigurable devices (FPGAs) and finally to reconfigurable or programmable architectures consisting of an array of coarse-grained elements such as functional units of fixed word size.

In order to handle the complexity of such highly integrated systems, they are preferably designed in a *top-down strategy* starting at the so-called *electronic system-*

#### 1. Introduction

Figure 1.1: Schematic representation of a system-on-a-chip (SoC). One possible realization of an accelerator could be a processor array. These arrays, either implemented as dedicated hardware for a single algorithm or in form of a programmable architecture, are the field of investigation in this thesis.

*level* (ESL). In [BMP07], Bailey, Martin, and Piziali define ESL as: *"The use of appropriate abstractions to increase comprehension of a system and enhance the probability of successfully implementing its functionality in a cost-effective manner, while meeting necessary constraints." Design decisions at system-level have the greatest influence on performance, cost, power consumption, and design time. Thus, ESL design is strongly related to the exploration of multiple possible solutions (<i>design space exploration*) [KSS<sup>+</sup>09]. Further, its integral view enables the early verification of a design specification. In order to reduce the time to market, mainly two approaches are pursued:

- 1. A *modular design principle* often referred to as *platform-based design* [KMN<sup>+</sup>00, SCDS04], where already designed components are systematically reused and assembled to an SoC.

- 2. *Synthesis* addresses (a), the automatic refinement of descriptions from one abstraction level to another; and (b), the translation of a behavioral description into a structural representation.

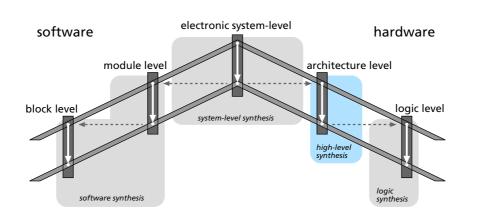

Both approaches seek expressive modeling and specification possibilities. Depending on the abstraction level (see Figure 1.2) and whether hardware or software is designed, different modeling and programming languages are used. On the hardware side, the description languages VHDL and Verilog are most widespread. For developing embedded software, common languages are assembler, C, C++, and Java. At

Figure 1.2: Abstraction levels for the design of embedded systems, adapted from Teich's *double roof model* [Tei97]. The upper roof denotes the behavioral view, the lower one the structural view. The present work focuses on high-level synthesis (marked in light blue).

the system-level, for the domain of digital signal and image processing, Matlab, C, C++, and SystemC are the languages of choice. Noteworthy about SystemC is that it tries to cover both sides, software and hardware [GLMS02]. Moreover, descriptions in SystemC can be successively refined for lower abstraction levels.

The synthesis at different abstraction levels is marked in Figure 1.2. The lower a synthesis type is placed on the *roof*, the older and more studied it is. For instance, logic synthesis can be traced back to the 19th century to the treatment of Boolean algebra, in addition the works in logic minimization by Shannon, Quine-McCluskey, or Karnaugh and Veitch are well-known. Thus, in the 1980s, logic synthesis was the first automated translation from Boolean equations to gate-level structures. Similar on the software side, the translation from assembly code to binary code is researched quite well. Some proponents of ESL design claim that the abstraction levels below system-level have been-similar to logic synthesis-mostly investigated. This is not true, since in academia as well as in industry there exists a great demand for high-level synthesis (also referred to as behavioral synthesis) methods that automatically transfer an algorithmic behavioral description into an efficient representation at register transfer level (RTL). High-level synthesis is a cutting-edge research topic with a multitude of challenges and open questions. This hypothesis is supported by a number of special sessions and workshops on this topic at recent premier electronic design automation conferences<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>For instance: Workshop *The New Wave of the High Level Synthesis* at Design, Automation and Test in Europe (DATE 2008); Workshop *High-level Synthesis: Back to the Future* at Design Automation Conference (DAC 2008); Workshop *High-Level Synthesis: Next Step to Efficient ESL Design* at Asia and South Pacific Design Automation Conference (ASP-DAC 2009).

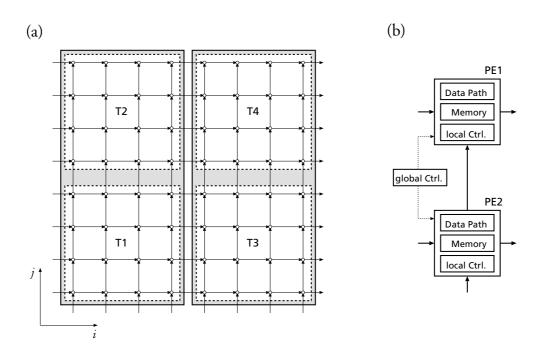

Figure 1.3: In (a), a two-dimensional iteration space consisting of 64 iterations and its hierarchical structuring into different subspaces, denoted by the white and gray tiles, is depicted. In (b), a corresponding dedicated hardware implementation with two processing elements is schematically shown.

The major challenges in high-level synthesis are:

- Domain-specific **models** and **languages** that preserve the parallelism of an initially given mathematical description.

- **Parallelization techniques** in order to exploit computationally intensive algorithms in the best possible way and **mapping methods**, which are able to target the hardware complexity of todays technology.

- Scheduling and allocation techniques that enable a holistic treatment of parallelism at different levels with simultaneous consideration of resource constraints and different requirements on performance, power consumption, and cost.

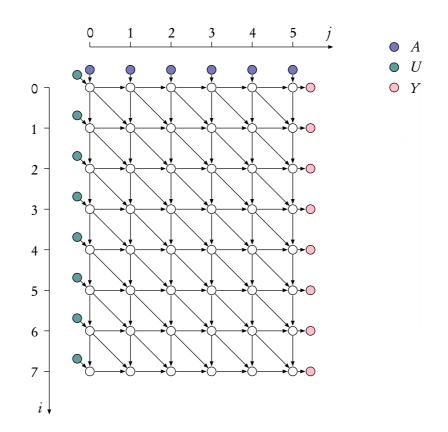

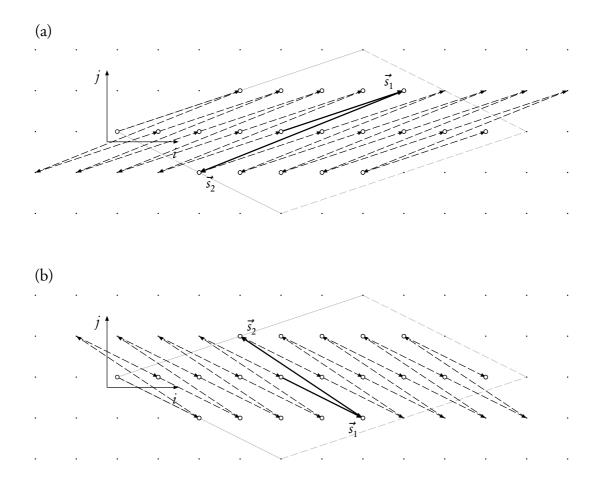

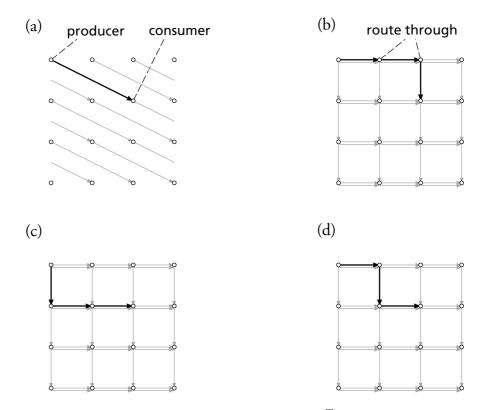

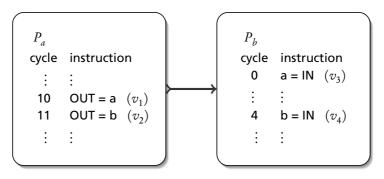

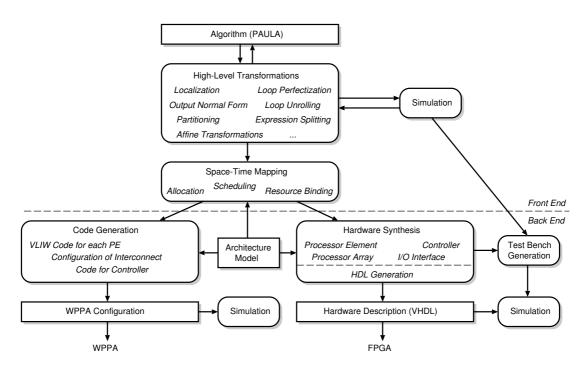

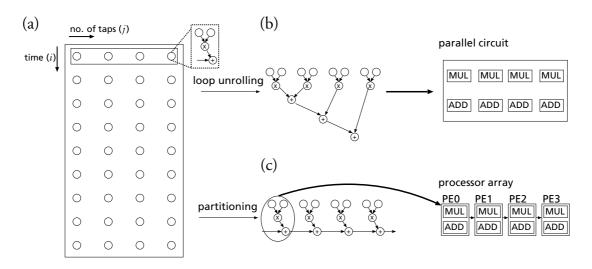

To overcome these very general challenges for arbitrary target architectures, we present a domain-specific methodology for so-called *processor arrays* in this thesis instead. The approach is focusing on computationally intensive algorithms with mostly regular and multi-dimensional data flow. The considered algorithms are expressed by nested loop programs. A wide variety of algorithms from the areas of digital image (e.g., median filter, 2-D convolution, edge detection), video (for instance, motion detection or motion compensation as in MPEG) and other signal processing (FIR, IIR, Kalman, and many more filters, linear predictive coding, discrete Fourier transform, etc.), linear algebra (matrix-vector multiplication, matrix multiplication, LU decomposition, matrix inversion, solving linear systems, etc.), combinatorial problems (e.g., shortest path problems or transitive closure problems), and many other scientific computing domains can be expressed by such loop programs. These processor arrays are typically tailored to the requirements of just one algorithm. This means, that the processors are not re-programmable for another application and thus, we are referring to them as processing elements (PE) in the course of the thesis. The regularity of the algorithms is reflected by the resulting processor arrays, whose structure corresponds to different levels of parallelism, memory, and control. An example is shown in Figure 1.3, where in (a) a 2-dimensional iteration space is visualized, which corresponds to a two nested loop. Each white point corresponds to the execution of a number of operations within the loop body. The arcs denote data dependencies between different iterations (also known as loop-carried dependencies) and inputs/outputs, respectively. Based on a given specification, a dedicated hardware accelerator should be implemented. Assuming that analysis of the performance requirements, memory and I/O cost leads to a *hierarchical partitioning* of the computations denoted by the two types of rectangles in Figure 1.3(a), then this partitioning corresponds to a hardware realization with two processing elements drafted in Figure 1.3(b). The iterations within the white tiles T1 and T2 are processed by the two elements PE1 and PE2. Once processing element PE1 has finished its execution of the 16 iterations within tile T1, it continues with tile T3; just as PE2 proceeds with tile T4 after finishing its work on T2. Such a hierarchical approach is not unusual since hereby communication cost can be traded for the cost of memory on several levels [BCD94, EM99, Eck01, HKV+07, BKV+08]. The assignment of iterations to processing elements can be seen as *global allocation*, but it scarcely says something about the schedule. Similarly, types and number of functional units inside the processing elements form a *local allocation*. Local and global control structures orchestrate the interplay of processing elements and functional units, respectively. For the considered class of algorithms, explicitly defined execution orders and static resource allocation are used in order to increase performance and to reduce cost. Memory and interconnect structures can be generated according to the required demands. Consequently, a customized hardware, dedicated to the acceleration of the given loop program, is derived.

The term *processor array* is often associated equally with the term *systolic array* [KL78]. The example in Figure 1.3, which considers several levels of allocation and parallelism into account, is yet far beyond the concepts in systolic array design.

#### 1. Introduction

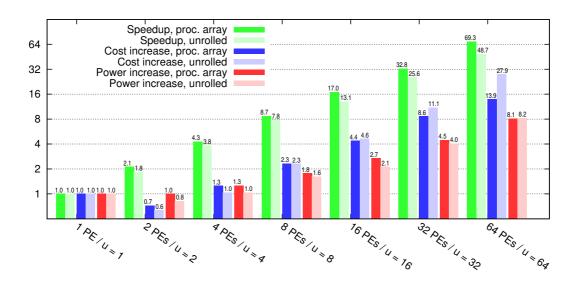

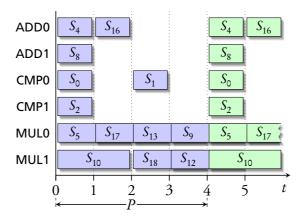

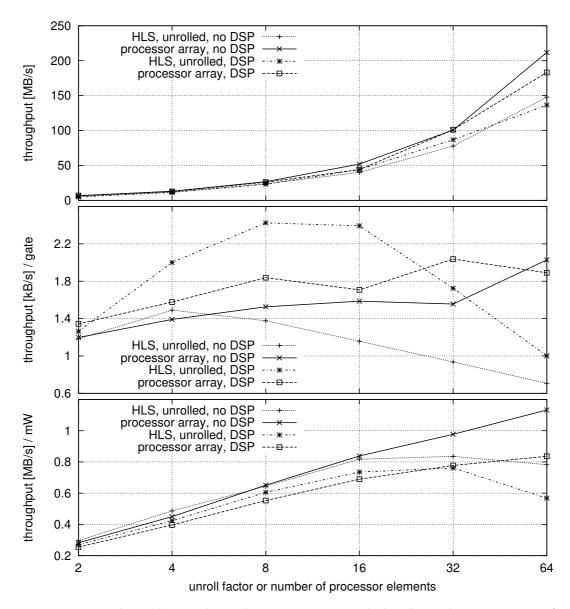

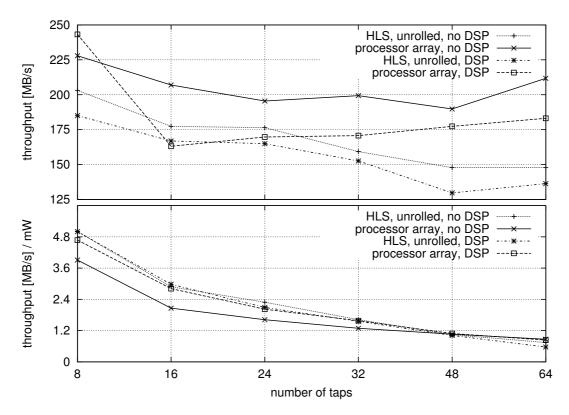

Figure 1.4: The speedup (with respect to throughput), cost and power increase for different 64-tap FIR filter implementations in relation to a sequentialized implementation, where only a single processing element with one multiplier and one adder is available, is shown. The x-axis shows the number of available resources (multipliers and adders), which is doubled from experiment to experiment. That means, in the case of the processor array approach, the values on the x-axis correspond to the number of PEs, and in the case of loop unrolling, the values on the abscissa match the unroll factor u.

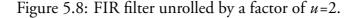

As mentioned earlier, processor arrays are a powerful instrument to exploit parallelism on several levels. Whereas other high-level synthesis approaches often offer no parallelization at all, or they use *loop unrolling* in order to achieve a higher data throughput. The PARO synthesis tool [HRDT08], which has been developed within the scope of this thesis, is able to perform both loop unrolling and the processor array approach. Internally, it employs the same techniques for resource allocation and scheduling, hence a fair quantitative comparison between the two approaches can be performed. In Figure 1.4, such a comparison is shown for different 64-tap FIR filter implementations. Although at this point of the thesis only briefly explained, several experiments with different numbers of available resources were performed and implemented in FPGA technology. The speedup characterizes the performance gain with respect to the throughput for the FIR filter algorithm. The cost increase is related to the gate count of the designs. In the single PE solution of the FIR filter, the 64 iterations are executed sequentially within one PE. For this solution, both throughput and cost are normalized to 1.0. Partitioning the algorithm to 2, 4, ..., 64 PEs theoretically also enables a higher throughput by the same factor. The super-

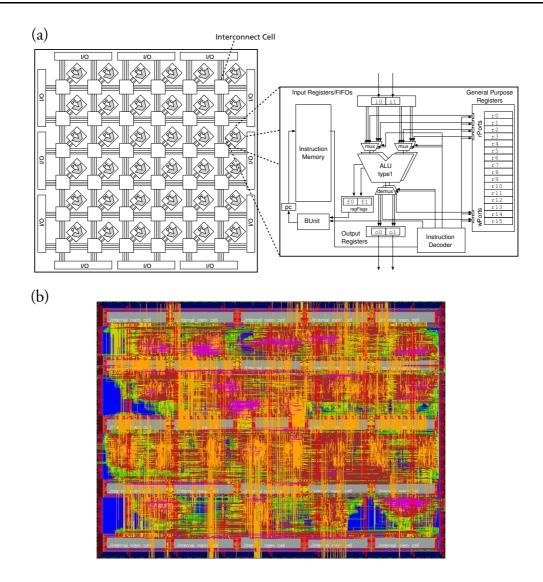

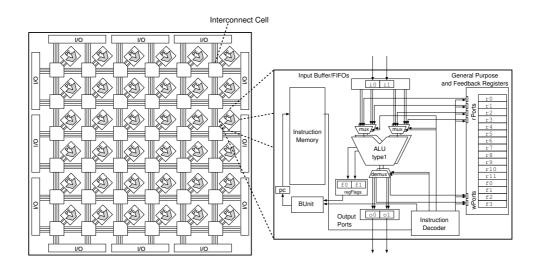

Figure 1.5: Processor array architecture of the class of so-called *weakly-programmable processor arrays* (WPPA) [HDK+05, KHKT06b]. In (a), the schematic array architecture and processor structure are depicted. A chip layout of a WPPA in 90 nm standard cell technology is shown in (b).

linear speedup in case of the processor array implementations is due to the increasing clock frequency for larger numbers of PEs. The moderate cost and power increase is caused by the decreasing amount of intermediate data, which have to be stored internally in the processor array. The results in terms of performance, area cost, and power of the two approaches clearly advocate the processor array approach.

Dedicated hardware accelerators can always outperform standard embedded processors in terms of performance and power consumption. Because of this, increas-

#### 1. Introduction

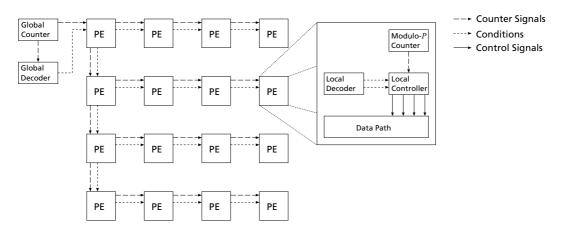

ingly more and more unconventional processors are emerging, which try to combine the best of both worlds: The performance, cost and power efficiency of dedicated hardware with the flexibility of programmable processors. These architectures typically consist of an array of reconfigurable, or to some extent programmable, coarsegrained units for data processing, few distributed memory, and a tightly interconnected communication network. An example of such an architecture is shown in Figure 1.5(a). Shown is an array of simple VLIW processors, each having its own small instruction memory and register file, however, with no shared memory access. A reconfigurable, switched interconnect allows communication on cycle basis. The parallelism of the architecture is expressed on different levels: several parallel working processors (loop-level parallelism), multiple functional units within one processor (instruction-level parallelism), and software pipelining. From the structural point of view, these programmable architectures are very similar to the dedicated processor arrays derived by high-level synthesis. Thus, it would stand to reason that similar or even the same concepts of algorithm modeling, allocation, and scheduling might be used for both kinds of processor arrays (dedicated as well as programmable accelerators).

### 1.1 Contributions and Bibliographic Notes

The dissertation's primary contributions are in the fields of *modeling* and *scheduling and allocation* techniques for high-throughput loop accelerators. The major achievement is a unified mapping methodology [DHT06d, DHT06c, DHK+07, THR+07, HRDT08] for computationally intensive programs, that targets dedicated hardware accelerators [HT01, RDHT05, DHT05, DHT+06e, DHT06b, DHT06a, DHRT07, HRDT08, DHT08, HDT09, DHT09, KDH+09, DZHT09], special classes of coarse-grained, reconfigurable architectures [HDT04a, HDT04b, HDT06, ESO+08], and tightly-coupled, programmable processor arrays [HDK+05, KHK+06a, KHK+06b, KHKT06a, KHKT06b, KHKT06c, KHK+06c, KHK+07, KKHT07, KHT07] and [DKH+09, KHKT08, KSHT08, KSHT09]. The major contributations of this thesis are summarized briefly in the following. They, include advances in modeling, parallelization, and scheduling as well as high-level synthesis.

**Modeling.** In order to map computationally intensive programs onto tightly-coupled processor arrays in a systematic way, a profound mathematical model is essential. In this context, a new class of algorithms called *dynamic piecewise linear algorithms* [HT04b, HT04c, HRDT08] and a corresponding graph representation for modeling iterative, multi-dimensional data flow is presented in the thesis. The class of dynamic piecewise linear algorithms extends well-known models, that are based on systems of

recurrence equations, defined over polyhedral iteration domains. Common to all existing approaches is that data dependencies are assumed to be static. Dynamic piecewise linear algorithms are able to model also a specific type of dynamic data dependencies, that is, dependencies becoming known only at run-time. By this enhancement, the range of applications with multi-dimensional data flow that can be parallelized and mapped onto massively parallel processor arrays is significantly increased. For instance, many computationally intensive applications for video and image processing consist of nested loop programs with only few and simple run-time dependent conditions.

On the basis of the class of dynamic piecewise linear algorithms, a novel programming language is presented in the thesis. The language is called PAULA [HRT08, HRDT08] and capable to model data flow dominated applications. It is intended for designing highly parallel applications, expressing parallelism at instruction, data, and loop level. The PAULA language allows very compact and efficient behavioral descriptions and serves as design entry when generating dedicated hardware accelerators [HRDT08], or might be used as high-level programming language for tightlycoupled multi-processor architectures [KHKT06b, THR<sup>+</sup>07]. The language covers a broad range of applications from the areas of digital image, video and other signal processing, linear algebra, cryptography, and many other scientific computing domains, where efficient parallelization techniques and hardware accelerators are indispensable.

Key features of the PAULA language are:

- A *functional programming language* dedicated to mapping computationally intensive algorithms onto parallel, tightly-coupled processor architectures. A full static single assignment form—also for *multi-dimensional arrays*—is provided.

- Powerful expressions to specify polyhedral and lattice iteration domains.

- Convenient usage of *big operators* such as  $\sum$  or  $\prod$ .

- Can handle *run-time dependent control flow* (support of dynamic piecewise linear algorithms).

- Besides *behavioral description* possibilities, also *architectural modeling* can be considered.

- Its applicability has been demonstrated in real-world case studies.

#### 1. Introduction

**Scheduling and Allocation.** As mentioned earlier, allocation and scheduling are the basic problems of high-level synthesis. However, scheduling with resource constraints can quickly become a hard combinatorial problem. In that case, often heuristics are deployed or a hierarchical approach according to the different structural levels is used. A hierarchical scheduling approach could lead to suboptimal results. Consider for instance, that all operations of a loop body are scheduled first (local schedule) and afterwards, a schedule for the iterations of a loop is determined (global schedule). Even when overlapping the different iterations afterwards, this could be worse compared to considering the instruction-level and the loop-level simultaneously as for instance in *modulo scheduling* [RST92]. Whereas modulo scheduling deals only with single processors and one-dimensional data dependencies, in the processor array approach we have to deal with arrays of processors, multi-dimensional data flow, and maybe several partitioning levels (cf. Figure 1.3). Hence, if the execution of not all of these parallelism levels is interleaved, the performance loss might accumulate.

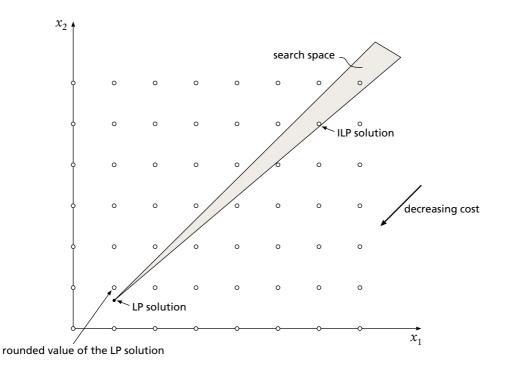

In this dissertation, exact and holistic scheduling techniques are developed that incorporate both, the local and the global allocation. By this close integration, performance optimal schedules may be derived. In order to obtain these schedules, an approach based on *mixed linear integer programming* (MIP) [NW99, HT01] is developed. In this thesis, the local schedule as well as the global schedule for several levels of partitioning is optimized for the first time, simultaneously. As depicted in Figure 1.3(a), the iterations within a white tile should be executed sequentially. In this context, a new *serialization constraint* for MIP is presented that leads to better schedules than existing approaches. The second main contribution in the area of scheduling is the formulation of resource constraints that take the mutual exclusivity of *iteration dependent conditions* as well as of *run-time dependent conditions* into account as shown in the following program fragment.

```

par (i >= 0 and i <= N-1)

{ // Equations with iteration dependent conditions

c[i] = a[i] * b[i] if (i == 0);

c[i] = a[i] * b[i] + c[i-1] if (i >= 1);

d[i] = c[i] > 255;

// Equation with run-time dependent condition

e[i] = ifrt(d[i], c[i], 255);

}

```

Shown is a PAULA program describing a dynamic piecewise regular algorithm. The **ifrt** statement selects in dependence on the value of the Boolean variable d[i] if the value of c[i] or the constant (255) is assigned to variable e[i].

In the context of the algorithm classes based on multi-dimensional recurrence equations, *conditional scheduling* [HT04a, HT04b, HT04d] has been applied for the first time within this work in order to schedule run-time dependent conditions.

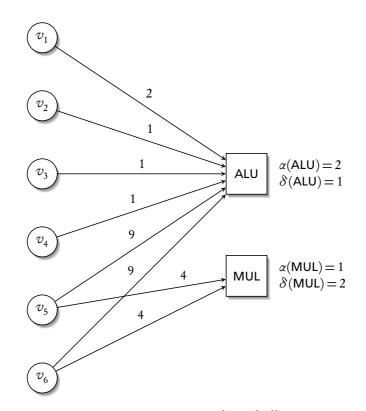

In addition, the MIP-based techniques have been extended by further constraints to cope with the constraints induced by a given fixed size programmable processor array (see Figure 1.5). These constraints consider local *register constraints* within the processors such as different types and numbers of available registers, and *channel constraints* of the communication structure such as the number of I/O ports of a processor element.

A modular scheduling concept is presented that can also be combined with techniques for channel routing [SMHT06, WKTH08c, WKTH08b, WKTH08a] and *subword parallelism* [SMHT08].

In addition, a number of other results have been contributed, which are not exactly in the scope of this doctoral thesis. These works include the following research areas:

- Methods for distributed loop control for non-rectangular processor array architectures [BHT01, BHT02],

- Energy estimation and optimization for dedicated processor arrays, which are obtained by projection as algorithm mapping [HT02a, HT02b, HT04a],

- High-speed simulation at register transfer level [KHT04b, KHT04a],

- I/O serialization for processor arrays [HT05],

- Defragmentation of the module placement in partially reconfigurable devices [vFM<sup>+</sup>05],

- Symbolic feasibility testing during the design space exploration of heterogeneous multi-processor systems [SHHT05],

- Rapid and virtual prototyping of system-on-chip designs [KKH+06, LHT09],

- Acceleration of multiresolution imaging algorithms on graphics and Cell processors [MKD+09, MHDT09].

### **1.2** Organization of the Thesis

The thesis is organized as follows:

Chapter 2 reviews related work on modeling of structured computations and considered algorithm classes in the polytope model, which are essential in the course of the thesis. Subsequently, our achievement, a novel algorithm class that allows to model recurrence equations with run-time dependent conditions, is presented. Afterwards, an overview of languages for parallel programming is given. With this background, the novel functional programming language PAULA, which is based on the newly introduced algorithm class, is presented.

Chapter 3 presents contributations on scheduling and allocation of dynamic piecewise linear algorithms. It provides the major methodological results of the thesis. Here, related work in the fields of allocation, loop parallelization, and scheduling is presented first. Following, some basic definitions and concepts for mapping nested loop programs are presented. After these fundamentals, a modular concept for scheduling nested loop programs is conceived. The developed scheduling methods are based on mixed integer programming.

Chapter 4 discusses how the information obtained during the allocation and scheduling phases (Chapter 3) can be utilized in order to generate program code for a given target architecture. The range of considered target architectures include as well dedicated hardware accelerators as weakly-programmable processor arrays. In this context, the PARO design system, which has been developed in the course of the thesis, is briefly described. In addition, high-level synthesis approaches and tools with emphasis on array processors are reviewed.

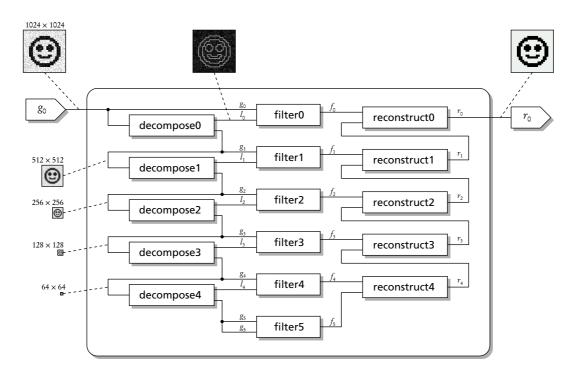

After this presentation of new scheduling techniques and the description of the PARO design system, Chapter 5 provides several experimental results by applying the new methods to different examples and a number of algorithms chosen from different benchmarks. Furthermore, a comparison, in terms of performance, area and power cost, of loop unrolling with our proposed method of loop partitioning is given. A complex real world application for image processing is presented in this chapter.

Finally, concluding remarks and directions of future work are presented in Chapter 6.

# Chapter 2

# Modeling

Loops are the major source of parallelism in most programs. For instance, many scientific and digital signal processing programs spend a large fraction of the overall computing time in loops [Knu71,SMN<sup>+</sup>03]. In order to accelerate these applications by use of parallel computation, either in software or hardware, loop parallelization techniques are required.

In this chapter, a formalism of recurrence equations, introduced by Karp, Miller, and Winograd [KMW67], is recapitulated, and related work on structured computations and algorithm classes in the polytope model [Len93, Fea96], that build upon this formalism, are discussed. All these models render important contributions in the area of loop parallelization, but have also limitations. Therefore, subsequently, our achievement, a novel algorithm class that allows recurrence equations with run-time dependent conditions, is presented.

Afterwards, an overview of languages for parallel programming is given. With this background, we present a new functional programming language based on the afore proposed algorithm class, which is tailored to our needs: The efficient specification and parallelization of loop programs for mapping them onto processor array architectures.

The main contributions of this chapter can be summarized as follows:

- Related work in the fields of structured computations, algorithm classes in the polytope model (Section 2.1.1), and parallel programming languages (Section 2.2.1) in general, are reviewed.

- The novel algorithm class of *dynamic piecewise linear algorithms* and a new model for *reduced dependence graphs* is presented in Section 2.1.2 and 2.1.4, respectively.

• The PAULA language that reflects the properties of the class of dynamic piecewise linear algorithms and many further concepts, such as reductions and full static single assignment form for multi-dimensional data flow, is presented in Section 2.2.2.

## 2.1 Structured Computations and Algorithm Classes in the Polytope Model

In 1967, Karp, Miller, and Winograd [KMW67] introduced in their seminal work on structured computations, the notion of a *system of uniform recurrence equations* and the concept of *dependence graphs*<sup>1</sup>. This concept provides a compact mathematical representation of the computations. In addition, the degree to which a computation can be processed in parallel, is characterized. Karp and others studied computation processes for solving partial differential equations by finite difference methods. Later, recurrence equations were often used for the specification of socalled *systolic* algorithms and arrays. The term *systolic array* dates back to Kung and Leiserson [KL78]. In the field of medicine, *systole* describes the contraction of the heart chambers, which presses the blood out of the chambers. Thus, a systolic array is an analogy to the regular beating of the heart and the pumping of blood. Kung and Leiserson themselves write in [KL78]:

A systolic system is a network of processors which rhythmically compute and pass data through the system. Physiologists use the work 'systole' to refer to the rhythmically recurrent contraction of the heart and arteries which pulses blood through the body. In a systolic computing system, the function of a processor is analogous to that of the heart. Every processor regularly pumps data in and out, each time performing some short computation, so that a regular flow of data is kept up in the network.

Since the whole parallelism is explicitly given, a system of uniform recurrence equations is in this feature similar to the *single assignment form* of programming languages, which are discussed in Section 2.2. The representation in single assignment form is particularly suitable for algorithmic transformations and has the following properties:

• On each right hand side of an equation, an expression is given, which defines the value of the variable standing on the left hand side of the equation (defi-

<sup>&</sup>lt;sup>1</sup>Karp, Miller, and Winograd used the term *dependence graph*; but describe a folded graph that is commonly referred to as *reduced dependence graph*.

nition). Within the expression on the right hand side, other variables can be used (usage).

- Each variable exists at most once in the algorithm on the left hand side of an equation.

- For all specified equations in the algorithm, there exits a sequential execution order. That is, an order can be found where each equation, that defines a variable, appears before the usage of the variable.

- Variables that appear only on the right hand side of an equation, thus are only used but not defined, form the set of *input variables*. The other way around, variables, that are only defined but never used within the algorithm, form the set of *output variables*.

The following fragment of an algorithm is in single assignment form and consists of four statements. The variables a and b are input variables since they are only used. Similar, d and f are output variables since they are only defined.

$$c = a - 3$$

$$d = b + (c/10)$$

$$e = b \cdot c$$

$$f = 2e + (c - b)$$

The formalism of systems of uniform recurrence equations has been used in many works. Over the years, this formalism evolved by concepts such as affine dependencies or piecewise definitions. In their original works, sometimes the authors precisely define a new structured algorithm class and give a name to it. At other times, the authors slightly modify or simplify the details of the structure. A detailed survey of different classes of structured computations and algorithms is given in [Zeh96]. In the following section of related work, classes of structured computations are discussed, that can be found in literature quite frequently or that are of interest for this thesis.

### 2.1.1 Related Work

**Uniform Recurrence Equations.** As stated before, in 1967, for modeling and for understanding regular and iterative processes, Karp and others [KMW67] introduced the concept of a system of uniform recurrence equations (SURE). Here, the authors consider problems associated with the evaluation of a system of k functions  $a_1(I), a_1(I), ..., a_k(I)$ . Each function  $a_i(I), i \in [1..k]$  is quantified for all points

$I \in \mathcal{I}$ , where  $\mathcal{I}$  is an integral subset  $\mathcal{I} \subseteq \mathbb{Z}^n$ . The values of  $a_1(I), a_1(I), \dots, a_k(I)$  have to satisfy a system of k recurrence equations having *uniform dependencies*. First, we consider the case k = 1 in order to explain a uniform dependency. A single recurrence equation is of the form

$$a_1(I) = \mathcal{F}_1(a_1(I-d_1), a_1(I-d_2), \dots, a_1(I-d_k)),$$

where  $I \in \mathcal{I}$ ,  $d_j$ ,  $j \in [1..k]$  is an *n*-dimensional integer vector called *iteration vector*, and  $\mathcal{F}_1$  is a single-valued function. Any difference  $I - d_j$  is element of  $\mathbb{Z}^n$  and each vector  $d_j$  is constant, thus the equation is said to have *uniform dependencies*. With this, a system of uniform recurrence equations is generally given by

$$a_i(I) = \mathcal{F}_i(a_{i_1}(I-d_{i_1}), a_{i_2}(I-d_{i_2}), \dots, a_{i_k}(I-d_{i_k})).$$

An example for  $I \in \mathbb{Z}$  is defined by the following system of equations:

$$a_1(I) = \mathcal{F}_1(a_2(I), a_3(I-1))$$

$$a_2(I) = \mathcal{F}_2(a_1(I+1), a_1(I-2), a_3(I))$$

$$a_3(I) = \mathcal{F}_3(a_3(I-1))$$

Karp and others also studied the computability of SUREs [KMW67]. The computability of a SURE can be determined by whether there is a cycle of zero weight in the reduced dependence graph.

In the following and throughout the rest of the thesis, we use a slightly different terminology when considering recurrence equations. Namely, instead of functions  $a_i(I)$ , indexed variables  $x_i[I]$  are considered. Equations are quantified, that is, an equation defines the indexed variable on its left hand side for each value of the iteration vector I. The set  $\mathcal{I} \subseteq \mathbb{Z}^n$  of possible values of I is called *iteration space*. According to this, a *uniform algorithm* consists of a set of equations, that relate linearly indexed variables. In general, we write

$$x_i[I] = f_i(x_{i_1}[I - d_{i_1}], x_{i_2}[I - d_{i_2}], \dots, x_{i_k}[I - d_{i_k}]) \qquad \forall I \in \mathcal{I}$$

with  $\mathcal{I} \subseteq \mathbb{Z}^n$ ,  $d_{i_j} \in \mathbb{Z}^n$ ,  $j \in [1..k]$ , any difference  $I - d_{i_j} \in \mathbb{Z}^n$ , and  $f_i$  is an arbitrary function. For example,

$$a[i,j] = a[i,j-1]$$

$$b[i,j] = add(a[i,j], b[i-1,j])$$

$$c[i,j] = mul(b[i,j], b[i,j])$$

where the system of equations is defined for all *i* and *j* in  $\mathcal{I} = \{(i \ j)^T \in \mathbb{Z}^2 \mid 1 \le i \le 10 \land 2 \le j \le 8\}$ . Often, all data dependencies  $d_i$ ,  $1 \le i \le k$  are combined in one

dependence matrix  $D = (d_1 \ d_2 \ \dots \ d_k)$ . For the above example, the following dependence matrix would result, if the variables on the right hand side of the equations are considered top down.

$$D = \left( \begin{array}{rrrr} 0 & 0 & 1 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 \end{array} \right)$$

The importance and versatile applicability of SUREs is studied in a multitude of works. Examples of these include the work of Quinton [Qui84], Delosme and Ipsen [DI85, DI86], Schwiegelshohn and Thiele [ST87a, ST87b, ST88], Djamegni [Dja04, Dja06], and many further works [XL91, KR06, OSY06, DQR<sup>+</sup>09] for the implementation of systolic arrays and asynchronous architectures [EJP92]. Some authors [SF91] even focus only on uniform algorithms that consist of a single equation. SUREs serve not only as basis for the synthesis of systolic arrays but are also used for other parallel models of computation. For instance, the authors in [GJM00] use SUREs for computing the minimal memory size in a PRAM (parallel random access memory) model. In [HOPS05], SUREs are used for the generation of parallel algorithms for cluster and grid computing. Schaffer et alii start from SUREs to exploit architectures with sub-word parallelism [SMC03, SSM06, SM06a, SMC06].

Systems of uniform recurrence equations also form the basis for the high-level synthesis tool PICO-NPA [SAM<sup>+</sup>02] (further details follow in Section 4.1.1.2).

**Regular Iterative Algorithms.** The class of *regular iterative algorithms* (RIA) is a continuation of the SUREs, shaped by Rao in [Rao85]. The first extension is that, each quantified equation might be assigned a further restriction of its iteration domain. This restriction is defined by one, or a set of inequalities (intersection of half spaces) and is referred to as *iteration dependent condition* in the following.

**Definition 2.1** (Iteration dependent condition). A condition  $C^{I}(I)$  is called iteration dependent condition of an equation and can be equivalently expressed by  $I \in \mathcal{I}_{C} \subseteq \mathbb{Z}^{n}$ , where the space  $\mathcal{I}_{C}$  is an iteration space called condition space.

In addition, the iteration variables on the left hand side of an equation can have an offset and the iteration space  $\mathcal{I}$  is required to be convex. Then, each equation *i* is defined for all  $I \in \mathcal{I}$  as follows.

$$x_{i}[I+f] = \mathcal{F}_{i}\left(x_{1}[I-d_{1i}], x_{2}[I-d_{2i}], \dots, x_{k}[I-d_{ki}]\right) \quad \text{if } \mathcal{C}_{i}^{\mathrm{I}}(I)$$

In Example 2.1 the matrix multiplication of two square matrices ( $C = A \cdot B$ ) is described by a regular iterative algorithm.

Example 2.1.

| $a[i,j,k] = a_{ik}$                                         | if $j = 1$ |

|-------------------------------------------------------------|------------|

| $b[i,j,k] = b_{kj}$                                         | if $i = 1$ |

| a[i,j+1,k] = a[i,j,k]                                       | if $j < N$ |

| b[i+1,j,k] = b[i,j,k]                                       | if $i < N$ |

| $c[i,j,k] = a[i,j,k] \cdot b[i,j,k]$                        | if $k = 1$ |

| $c[i, j, k] = c[i, j, k - 1] + a[i, j, k] \cdot b[i, j, k]$ | if $k > 1$ |

| $c_{ii} = c[i, j, k]$                                       | if $k = N$ |

Many related work in the fields of loop parallelism [RK90, HH95] and data-path synthesis [AC94] is based upon this algorithm class. For further literature about the class of regular iterative algorithms, we refer to the overview in [RG06].

**Piecewise Linear Algorithms and Piecewise Regular Algorithms.** The class of *piecewise linear algorithms* (PLA) has been defined by Thiele and Roychowdhury in [TR91]. This class extends the notation of regular iterative algorithms. A piecewise linear algorithm consists of a set of N quantified equations,  $S_1[I], \ldots, S_i[I], \ldots, S_N[I]$ . Each equation  $S_i[I]$  is defined for all  $I \in \mathcal{I}_i$  and is of the following form.

$$x_i[P_iI + f_i] = \mathcal{F}_i(\dots, x_j[Q_iI - d_{ji}], \dots) \qquad \text{if } \mathcal{C}_i^{\mathrm{I}}(I)$$

where  $x_i$ ,  $x_j$  are affinely indexed variables. The so-called *indexing functions* of the variables are defined by the constant rational indexing matrices  $P_i$ ,  $Q_j$  and by the constant rational vectors  $f_i$ ,  $d_{ji}$  of corresponding dimension.  $\mathcal{F}_i$  denote arbitrary functions and the dots (...) denote similar arguments.  $I \in \mathcal{I}_i \subseteq \mathbb{Z}^n$  is a linearly bounded lattice (definition follows), called iteration space of the quantified equation  $S_i[I]$ . The set of all points  $P_iI + f_i$ ,  $I \in \{\mathcal{I}_i \cap \mathcal{C}_i^I(I)\}$  is called the index space of variable  $x_i$ .

A piecewise linear algorithm is called *piecewise regular algorithm* (PRA) [Thi88], if the matrices  $P_i$  and  $Q_i$  are the identity matrix.

An algorithm is in *output normal form* if  $P_i$  is the identity matrix and  $f_i$  is the zero vector.

These algorithm classes have been extensively studied by Teich and Thiele for the design of processor arrays [TT91, Thi92, Tei93]. A similar algorithm class, also able to handle affine data dependencies, is known as *system of affine recurrence equations* (SARE) [YC88, YC92, WS94, MP01].

Note that the transformation, maybe automatically, of affine data dependencies into uniform dependencies is called *localization*. Amongst others, localization techniques have been studied in the following works [TR91, Tei93, MMRR01, Eck01, MM04] and our work in [HT05].

It should be noticed, that many authors (for instance, [FM98,SMC00,MFMS03, GQR03, SM06b, SM06c, SM06d]) use the term SURE even if, according to the above taxonomy, RIAs or PRAs are meant.

**Further Algorithm Classes.** Roychowdhury and others introduced in [RTRK88] so-called *linearly indexed weak single assignment codes*. Here, the main novelty is the possibility to consider a generic operator on the right hand side of the equations. The operator is required to be associative and commutative, and is defined over several iterations. Examples of such operators are reductions, as for instance, summations or multiplications. This algorithm form is used for example by Eckhart in [EM99], although later he called this class *affine indexed algorithms* [Eck01].

Eventually, none of the aforementioned algorithm classes is powerful enough to specify *dynamic data dependencies*. This means, that branching of the program execution cannot depend on already computed variables. Only few results exist that incorporate specific run-time decisions. With regards to the loop bounds, the authors in [GGL99] propose an approach, which can handle while-loops. The method has been integrated in the parallelizing compiler LooPo [GL96]. In [Meg93] and [AR94], the authors study also a class of run-time dependencies. Their work studies dynamic programming for knapsack problems by consideration of indirect addressing. Furthermore, the authors show how optimal systolic array-like implementations can be derived. In [SD03,Ste04], the authors present a method to derive a so called *dynamic single assignment code* (dSAC), based on *fuzzy array data flow analysis* [CBF95]. The difference compared to single assignment code, where every left hand side variable is written exactly once, is, that in dSAC every variable is written at most once. That means, at compile-time, it is unclear whether a variable will be defined during the program execution.

### 2.1.2 Dynamic Piecewise Linear/Regular Algorithms

In order to consider and systematically map not only algorithms with iteration dependent conditions, which are static and known at compile time, in the following, we extend the algorithm class to allow for *run-time dependent conditions*.

**Definition 2.2** (Run-time dependent condition). *A* run-time dependent condition *is a Boolean variable*  $C^{\text{RT}}[I]$  *of the form*

$$\mathcal{C}^{\mathrm{RT}}[I] = \mathcal{F}_{\mathcal{C}}(\dots, x_{j}[Q_{j}I - d_{j}], \dots)$$

where  $\mathcal{F}_{C}$  denotes an arbitrary Boolean-valued function involving constants and linearly indexed variables only.

Typically, the function  $\mathcal{F}_{\mathcal{C}}$  of a run-time dependent condition describes a relational operator such as =, >, ≥, <, ≤, or,  $\neq$ .

**Definition 2.3** (Dynamic Piecewise Linear/Regular Algorithms [HT04b]). A dynamic piecewise linear algorithm (DPLA) is a PLA where the following extended type of equations expresses run-time dependent definitions of computations as follows:

$$x_i[P_iI + f_i] = \begin{cases} \mathcal{F}_i^1(\dots, x_j[Q_jI - d_{ji}], \dots) & \text{if } (\mathcal{C}_i^{\mathrm{I}}(I) \land \mathcal{C}_i^{\mathrm{RT}}[I]) \\ \mathcal{F}_i^{\mathrm{o}}(\dots, x_k[Q_kI - d_{ki}], \dots) & \text{if } (\mathcal{C}_i^{\mathrm{I}}(I) \land \neg \mathcal{C}_i^{\mathrm{RT}}[I]) \end{cases}$$

The notation  $\neg C_i^{RT}[I]$  denotes the negation of the run-time dependent condition  $C_i^{RT}[I]$ , which is similar to the else-branch of an if-condition. We introduce intermediate variables  $x_i^1[P_iI + f_i] = \mathcal{F}_i^1(...)$  and  $x_i^0[P_iI + f_i] = \mathcal{F}_i^0(...)$  to express the conditional definition of  $x_i[P_iI + f_i]$ . A DPLA is called dynamic piecewise regular algorithm (DPRA) if the matrices  $P_i$ ,  $Q_j$ , and  $Q_k$  are the identity matrix.

Note that by this definition we can strictly partition each condition into an iteration dependent condition and a run-time dependent condition (*separability*). Because of both, the run-time dependent condition ( $C_i^{\text{RT}}$ ) and the negated run-time dependent condition ( $\neg C_i^{\text{RT}}$ ), the variable on the left hand side of an equation is defined whensoever  $C_i^{\text{I}}(I)$  is fulfilled and thus, the computability property of a program remains satisfied. The definition of a variable in either case is the main difference compared to the approach presented in [SD03, Ste04] where not both cases have to be defined.

For illustration, two small examples are given. The first is a DPRA and the second describes a DPLA. The iteration space is omitted in each case.

#### Example 2.2.

$$x[i] = \begin{cases} 2 \cdot \frac{\cos(y[i-1])}{\sin(x[i-1])} & \text{if } (x[i-1] \neq 0) \\ \infty & \text{if } (x[i-1] = 0) \end{cases}$$

Example 2.3.

$$x[i,j] = \begin{cases} x^{1}[i,j] & \text{if } (\mathcal{C}^{\mathrm{RT}}[i,j] \land (i > 0 \land j \le 3)) \\ x^{0}[i,j] & \text{if } (\neg \mathcal{C}^{\mathrm{RT}}[i,j] \land (i > 0 \land j \le 3)) \end{cases}$$

$$x^{1}[i,j] = y[i,j] \land z[2i-1,j] \\ x^{0}[i,j] = y[i,j] \\ \mathcal{C}^{\mathrm{RT}}[i,j] = (z[2i-1,j] > 1)$$

### 2.1.3 Iteration Spaces

So far, the possible domains of definition for the algorithms have not been formalized, except that we stated sometimes these iteration spaces have to be convex or an n-dimensional integral set. Formally, an iteration space is defined as follows.

**Definition 2.4** (Iteration space). An iteration space  $\mathcal{I}$  is a set. Its elements are valid values for an index vector I. The iteration space is a discrete—not necessarily finite—set.

Throughout this thesis, we assume that the iteration space  $\mathcal{I}$  is an *n*-dimensional subset of integers,  $\mathcal{I} \subset \mathbb{Z}^n$ . Often, the terms *iteration space* and *index space* are used synonymously, however, we distinguish between the terms. The iteration space is the *domain*  $\mathcal{I}$  whereas the index space denotes the *codomain* when transforming the iteration space by an index function.

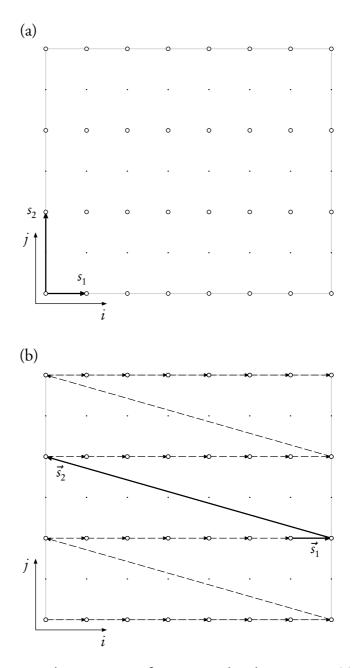

In loop programs, the iteration space is defined by the loop bounds. The iteration variables are generally increased or decreased by a constant value (regularity of the iteration space). If the loop programs are *perfectly nested*<sup>2</sup>, the iteration spaces are convex. Each loop bound defines a half space and the intersection of all half spaces describes a polyhedron or in case of boundedness a polytope. Loop parallelization in the polytope model is a powerful technique [Len93, Fea96], therefore in the following, the iteration spaces are formulated as polyhedra or even more general as so-called *linearly bounded lattices*.

**Definition 2.5** (Linearly bounded lattice [Tei93]). *A* linearly bounded lattice (*LBL*) *denotes an iteration space of the form*

$$\mathcal{I} = \{I \in \mathbb{Z}^n \mid I = Mx + c \land Ax \ge b\}$$

where  $x \in \mathbb{Z}^l$ ,  $M \in \mathbb{Z}^{n \times l}$ ,  $c \in \mathbb{Z}^n$ ,  $A \in \mathbb{Z}^{m \times l}$  and  $b \in \mathbb{Z}^m$ .  $\{x \in \mathbb{Z}^l \mid Ax \ge b\}$  denotes the set of integral points within a convex polyhedron or in case of boundedness within a polytope in  $\mathbb{Z}^l$ . This set is affinely mapped onto iteration vectors I using an affine transformation (I = Mx + c).

In [Tei93], it is shown that each set  $\mathcal{I} \subseteq \mathbb{Z}^n$  can be described as an LBL. Although this is an interesting result, at the same time, this possible generality, to represent an arbitrary *n*-dimensional, integral point set, could make the treatment of a given algorithm very complicated and inefficient. Thus, throughout the thesis, we assume that the matrix M is square and of full rank. Then, each vector x is uniquely mapped to an iteration point I.

Often, when the lattice matrix M is the identity matrix and the vector c is zero, the iteration space coincides with the following definition of a polyhedron.

$$\mathcal{I} = \{I \in \mathbb{Z}^n \mid AI \ge b\}$$

<sup>&</sup>lt;sup>2</sup>A loop nest is called *perfectly nested* if only the innermost loop contains statements.

### 2.1.4 Dependence Graphs

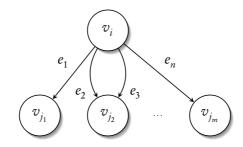

Another, geometric approach for modeling single assignment algorithms, is the representation by a *dependence graph*. For each variable instance at each iteration point  $I \in \mathcal{I}$ , there exists one node. Dependencies from one node (variable) to another are denoted by an edge in the graph. In detail, if there exists an edge from a node a[J] to a node b[K] with  $J, K \in \mathcal{I}$ , then b[K] needs the result of a[J] for its computation. Thus, a dependence graph expresses a partial order between the different operations of the algorithm. Since the iteration space of an algorithm can be arbitrarily large, also the graph can be arbitrarily large. If algorithms with uniform data dependencies are considered, the dependence graph is also regular and can be *folded* to a *reduced dependence graph* [Rao85, Thi88].

**Definition 2.6** (Reduced dependence graph). Let a uniform algorithm in output normal form be given with  $\mathcal{I} \subseteq \mathbb{Z}^n$ . Then a corresponding reduced dependence graph (RDG) G = (V, E, D) of dimension n has the following properties. There exists a set V of nodes and a set of edges  $E \subseteq V \times V$ . For each variable  $x_i$  of the algorithm exists one node  $v_i \in V$  in the RDG. In addition there exists a mapping  $E \mapsto D$  that assigns to each edge  $e = (v_i, v_j) \in E$  an n-dimensional dependency vector  $d_{ij} \in \mathbb{Z}^n$  if a variable  $x_j$  of the algorithm depends on a variable  $x_i$  of the algorithm.

As example, an algorithm for IIR filtering is considered, that is used for speech analysis and synthesis with *linear predictive coding* (LPC) [PM06].

Example 2.4.

$$z[i,j] = a[i,j] \cdot x[i-1,j-1]$$

$$b[i,j] = a[i,j] \cdot c[i,j-1]$$

$$c[i,j] = c[i,j-1] + z[i,j]$$

$$x[i,j] = x[i-1,j-1] + b[i,j]$$

where the iteration space is defined by  $\mathcal{I} = \{(i \ j)^T \in \mathbb{Z}^n \mid 1 \le i \le N \land 1 \le j \le M\}.$

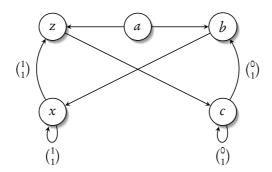

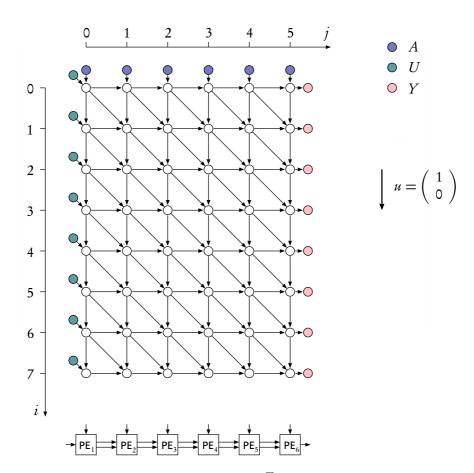

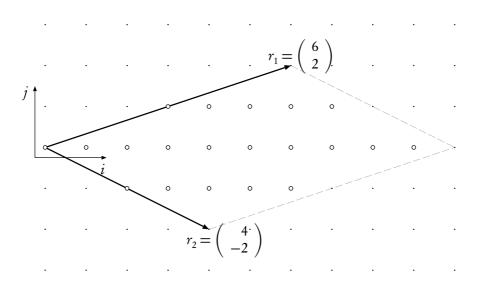

The reduced dependence graph of the algorithm in Example 2.4 is shown in Figure 2.1. Variables that depend on the same iteration have a zero dependency vector and are not annotated to the edges.

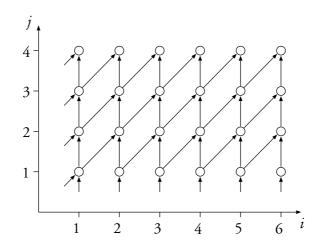

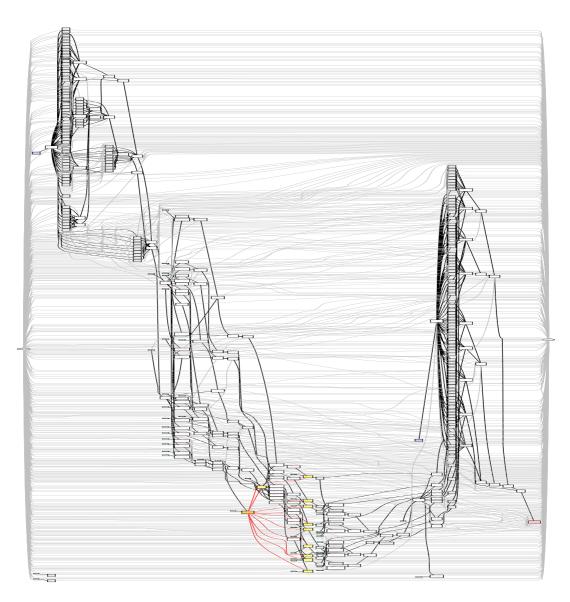

The *unfolded* dependence graph is shown in Figure 2.2, where the upper bounds of the iteration space are chosen to be N = 6 and M = 4. The regularity of the algorithm is clearly visible. The concepts of RDGs and uniform algorithms are closely related to each other. However, with Definition 2.6 of an RDG, it is not possible do describe algorithms that go beyond the concept of uniform recurrence equations. Thus, a more general definition is necessary.

Figure 2.1: Reduced dependence graph of the LPC algorithm given in Example 2.4.

Figure 2.2: Dependence graph of the LPC algorithm for N = 6 and M = 4.

**Definition 2.7** (Reduced dependence graph (extended)). Let a dynamic piecewise linear algorithm be given. Then each node  $v \in V$  of the corresponding reduced dependence graph (RDG) G = (V, E) might have several<sup>3</sup> of the following types.

- Normal: For each indexed variable on the left hand side of the algorithm, one node of type normal exists in the graph.

- Constant: For each constant within the algorithm, one node of type constant exists in the graph.

- Input: Variables that are only used in the algorithm or rather nodes that are only used in the graph are of type input.

- Output: Similar to the input type. Nodes, that are only defined but not used in the graph are of type output.

<sup>&</sup>lt;sup>3</sup>For instance, a node might be a merge node as well as an output node at the same time.

- Propagation: Similar to the normal type but no function or operation is associated to the node, only a copy operation/propagation.

- Condition: To denote a run-time dependent condition  $C^{\text{RT}}$ .

- Merge: A node to merge the data flow again after it was split up into different branches.

Also different edge types exist.

- Normal: An edge that denotes a data dependency from one node to another node.

- Constant: An edge that denotes the usage of a constant.

- Conditional: This type is used for outgoing edges of a node of type condition.

- Serialization: Denotes an artificial serialization between two nodes. That means, the serialization is not directly included in the originally given algorithm description but was added afterwards.

To each node of type normal, input, output, or propagation further attributes are associated. Namely, the iteration domain it is defined for and the indexing function of the variable. Moreover, a unique identifier, the variable name, and its functionality are annotated.

To each edge of type normal, the corresponding indexing function is annotated. Compared to the traditional definition of an RDG (cf. Definition 2.6), this also allows to represent affine data dependencies.

For illustration, the following example of an algorithm for matrix multiplication, consisting of six equations  $(S_1 \text{ to } S_6)$ , is considered.

#### Example 2.5.

$$S_{1}: \qquad a[i,j,k] = a_{in}[i,k] \qquad \text{if } j = 1$$

$$S_{2}: \qquad a[i,j,k] = a[i,j-1,k] \qquad \text{if } j > 1$$

$$S_{3}: \qquad z[i,j,k] = a[i,j,k] \cdot b_{in}[k,j]$$

$$S_{4}: \qquad c[i,j,k] = z[i,j,k] \qquad \text{if } k = 1$$

$$S_{5}: \qquad c[i,j,k] = c[i,j,k-1] + z[i,j,k] \qquad \text{if } k > 1$$

$$S_{6}: \qquad c_{out}[i,j] = c[i,j,k] \qquad \text{if } k = N$$

with  $\mathcal{I} = \{(i \ j \ k)^T \in \mathbb{Z}^3 \mid 1 \leq i, j, k \leq N\}$  as iteration space.

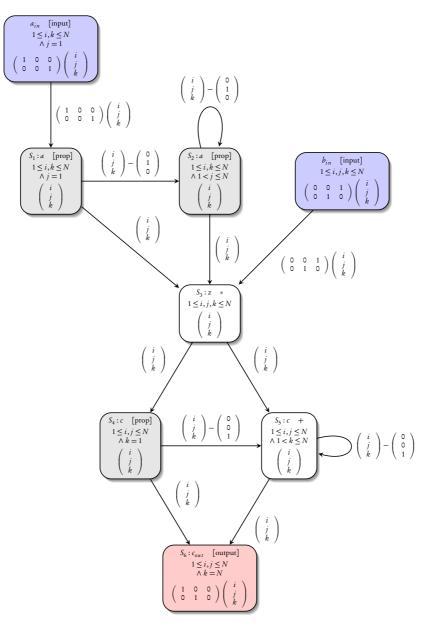

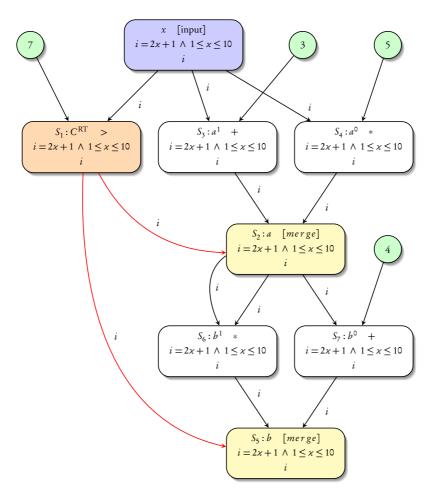

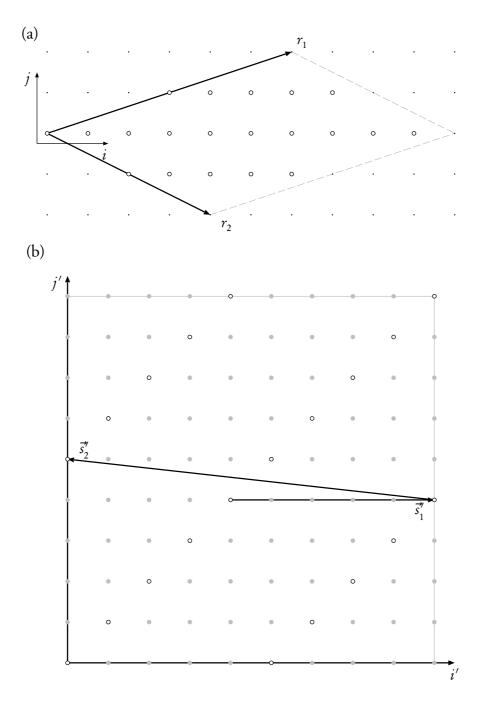

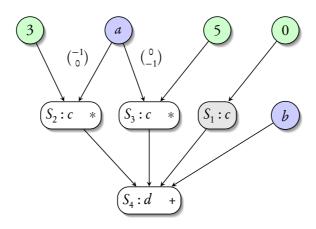

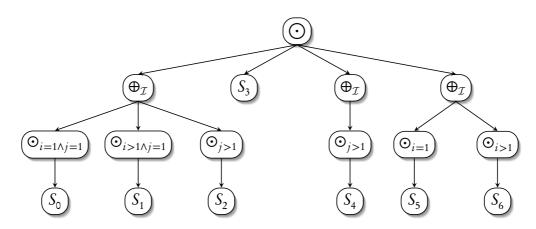

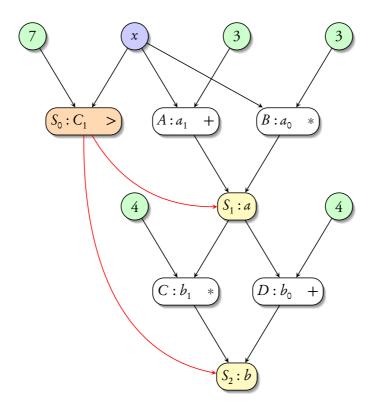

Figure 2.3: Reduced dependence graph for the matrix multiplication algorithm in Example 2.5

The corresponding RDG is shown in Figure 2.3. Here, different node types have different colors, input nodes are blue, output nodes are red, normal nodes are white, and propagations are colored gray. The distinction in terms of color between normal nodes and propagations only serves for better visibility in order to distinguish actual computations from propagations/assignments quickly. As can be seen, not all variables have to be embedded in the same dimension. For instance, the input variables

$a_{in}$  and  $b_{in}$  as well as the output variable  $c_{out}$  are only two-dimensional, whereas all other variables are three-dimensional. Note that this characterization possibility also allows to model piecewise defined algorithms and even parallel/communicating loop programs defined over different iteration spaces. This is a substantial difference compared to traditional approaches where the algorithm has to be embedded in a common global iteration space, which is derived by the convex hull of the union of iteration subspaces.

The next program fragment, in Example 2.6, depicts a dynamic piecewise regular algorithm, consisting of seven equations  $(S_1 \text{ to } S_7)$ .

### Example 2.6.

| $S_1$ :                 | $C^{\mathrm{RT}}[i] = (x[i] > 7)$                   |                                                                                 |

|-------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|

| <i>S</i> <sub>2</sub> : | $a[i] = \begin{cases} a^1[i] \\ a^0[i] \end{cases}$ | if $(\mathcal{C}^{\mathrm{RT}}[i])$<br>if $(\neg \mathcal{C}^{\mathrm{RT}}[i])$ |

| <i>S</i> <sub>3</sub> : | $a^1[i] = x[i] + 3$                                 |                                                                                 |

| $S_4$ :                 | $a^{\circ}[i] = x[i] \cdot 5$                       |                                                                                 |

| <i>S</i> <sub>5</sub> : | $b[i] = \begin{cases} b^1[i] \\ b^0[i] \end{cases}$ | if $(\mathcal{C}^{\mathrm{RT}}[i])$<br>if $(\neg \mathcal{C}^{\mathrm{RT}}[i])$ |

| <i>S</i> <sub>6</sub> : | $b^1[i] = a[i] \cdot a[i]$                          |                                                                                 |

| <i>S</i> <sub>7</sub> : | $b^{\circ}[i] = a[i] + 4$                           |                                                                                 |

with the LBL  $I = \{i \in \mathbb{Z} \mid i = 2x + 1 \land 1 \le x \le 10\}$  as iteration space.

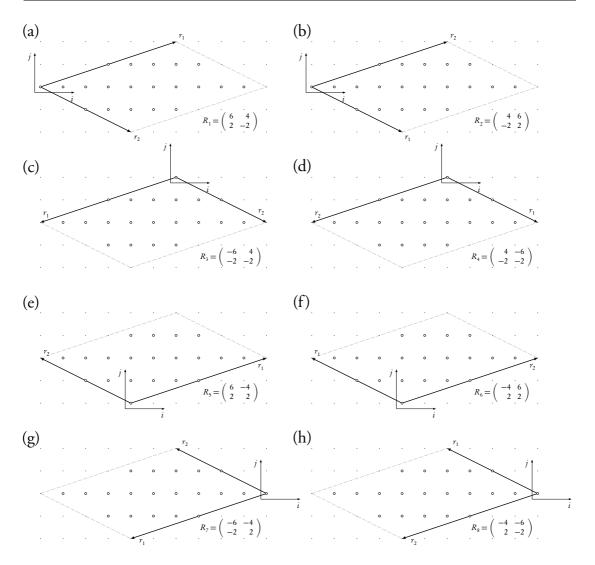

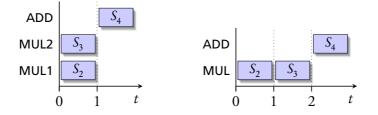

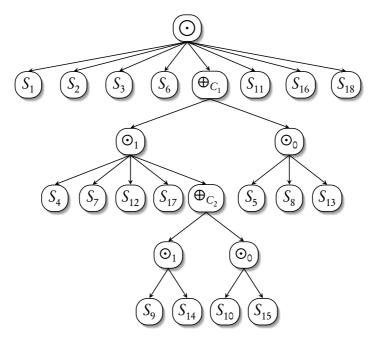

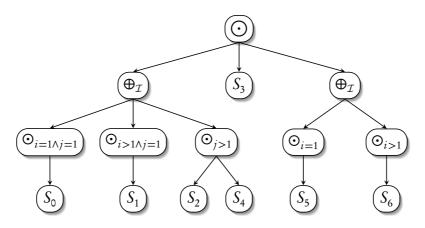

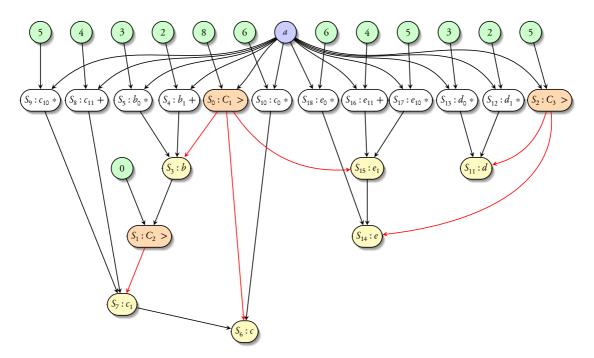

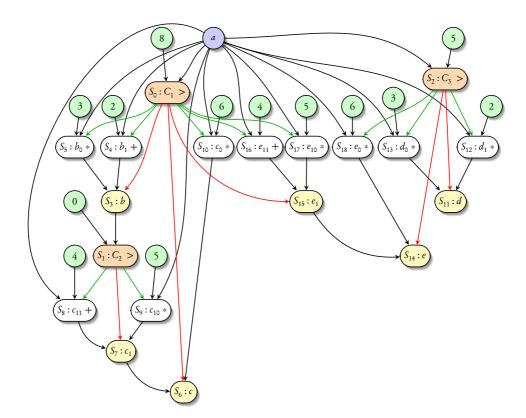

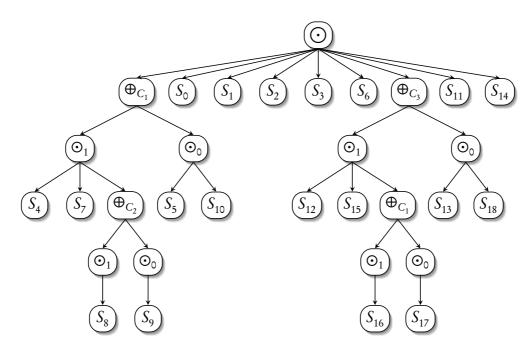

The corresponding RDG is illustrated in Figure 2.4. In this figure, constant nodes are colored green, conditions are colored orange, and merge nodes are shown in yellow. The results of the condition (Boolean value) are drawn as red edges to the merge nodes in order to select the right input.

# 2.2 Languages for Parallel Programming

Languages for parallel programming have a long tradition in parallel and high performance computing, but also when considering digital signal processing and data flow computing. The following section about related work gives only an overview with an emphasis on functional languages for data flow intensive and streaming applications.

### 2.2.1 Related Work

As mentioned in the introduction, there is a continuous trend to higher abstraction levels and the usage of high-level languages for the design of embedded digital sys-

Figure 2.4: Reduced dependence graph of the DPRA given in Example 2.6.

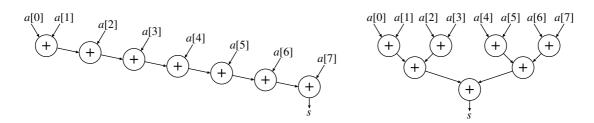

tems. However, starting with a sequential language such as C, C++, or SystemC has the disadvantage that their semantics force a lot of restrictions on the execution order of the program. Most of the parallelism contained in the original mathematical model of the algorithm is lost during the transformation to sequential code. For instance, a simple summation  $s = \sum_{i=0}^{7} a[i]$  is often written in C as a for loop in the following manner:

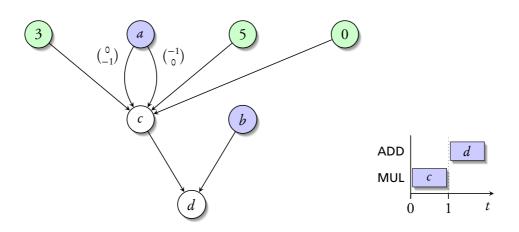

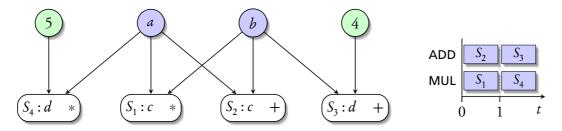

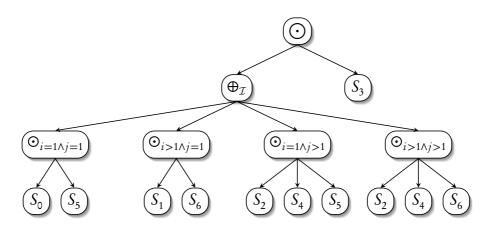

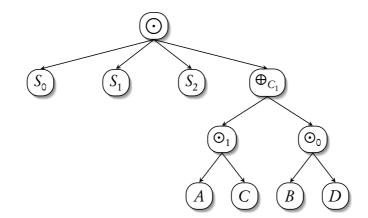

By this, a sequential order is already predefined and a later parallelization can become a crucial task. In Figure 2.5, the difference between a sequential and a parallel implementation shall be demonstrated. Granted that enough resources (adders) are available, the latency might be reduced from linear to logarithmic run-time. The

Figure 2.5: Sequential and parallel implementation of a sum consisting of eight summands.

mapping of such algorithms to massively parallel architectures requires data dependency analysis in order to make the inherent parallelism explicit. Still, this process is very complex, since sequential languages allow, that variables, once defined, can be overwritten arbitrarily. Another disadvantage of C-based hardware design is that most design tools support only a limited subset of the language. Porting existing, highly optimized C code to such an environment is a time consuming task and often ends in completely rewriting the code from scratch. In order to avoid this, modern software compilers like gcc [GCC09] as of version 4 or LLVM [LA04] use a so-called *static single assignment (SSA)* form as intermediate representation, where each variable is written exactly once. SSA allows the application of manifold compiler optimizations and transformations in a very efficient way. But since the SSA form is used only in the intermediate representation (basic block level), these compilers cannot solve the data dependence analysis problem for multi-dimensional arrays.